## introspect technology

Memory Interface Testing

July 2024

### Agenda

- 1. About Introspect Technology

- 2. Scope of This Presentation

- 3. ATE on Bench Architecture

- 4. Memory and Component Testing

- 5. Host Controller Testing

- 6. Protocol Analyzer and Interposer Systems

- 7. SV6E-X SidebandBus Controller and Tester

- 8. Summary

# About Introspect Technology

### Introspect Makes Tools for Engineers

#### ADDRESSING GAP IN TEST EQUIPMENT AVAILABILITY

- Bench-like accuracy and precision

- EDA style scripting

- Software-style regression and versioning Designation

- ATE-like speed

- Highly parallel

- Designed for automation

### We Test Electronic Interfaces...

**IMAGE SENSORS**

**MOTION SENSORS, MICROPHONES**, **SPEAKERS**

> **APPLICATIONS** PROCESSORS

**IR RANGE**

#### **POWER MANAGEMENT ICs**

#### **MEMORIES**

**RFICs**

### We Act as a Link Partner / Exerciser...

### And We Probe a Live System

introspect technology

### **Company Facts**

- Founded in 2012

- Offices in Montréal, Québec and Vancouver, British Columbia

- Global, outsourced sales and distribution channel

- Manufacturer of capital equipment used in the **design validation** and **mass production testing** of electronic components that contain high-speed communications interfaces

- Smartphones

- Personal computers and tablets

- Augmented reality headsets

- Automotive systems and self-driving systems

- Data center server racks

- Medical equipment

# Scope of This Presentation

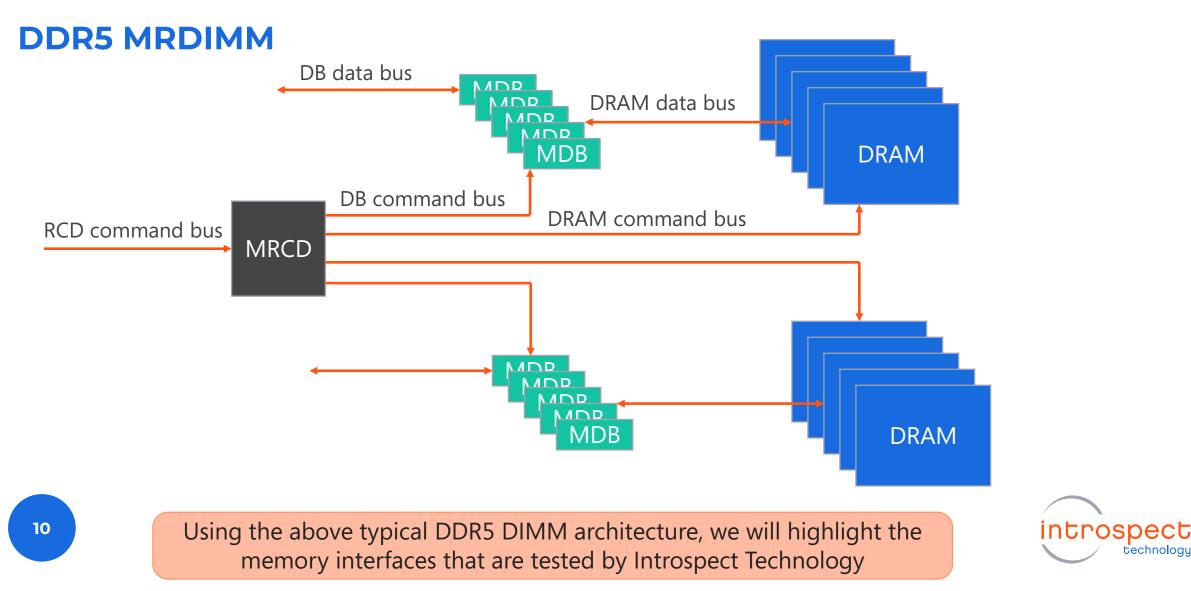

### Validating Memory Interfaces

technologi

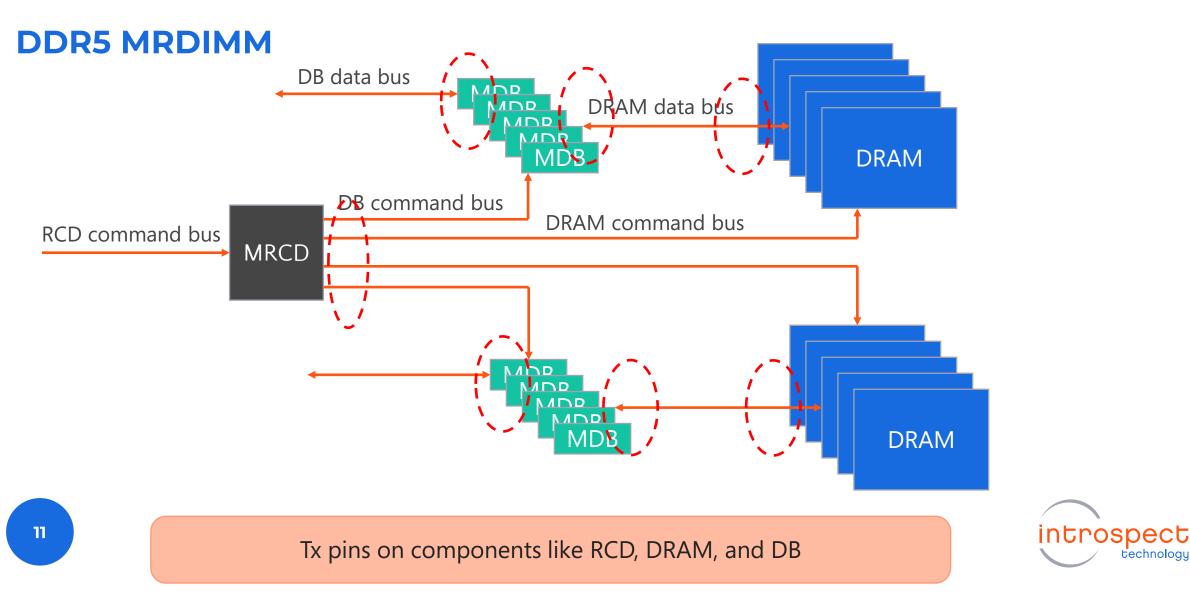

### Transmitter Interfaces

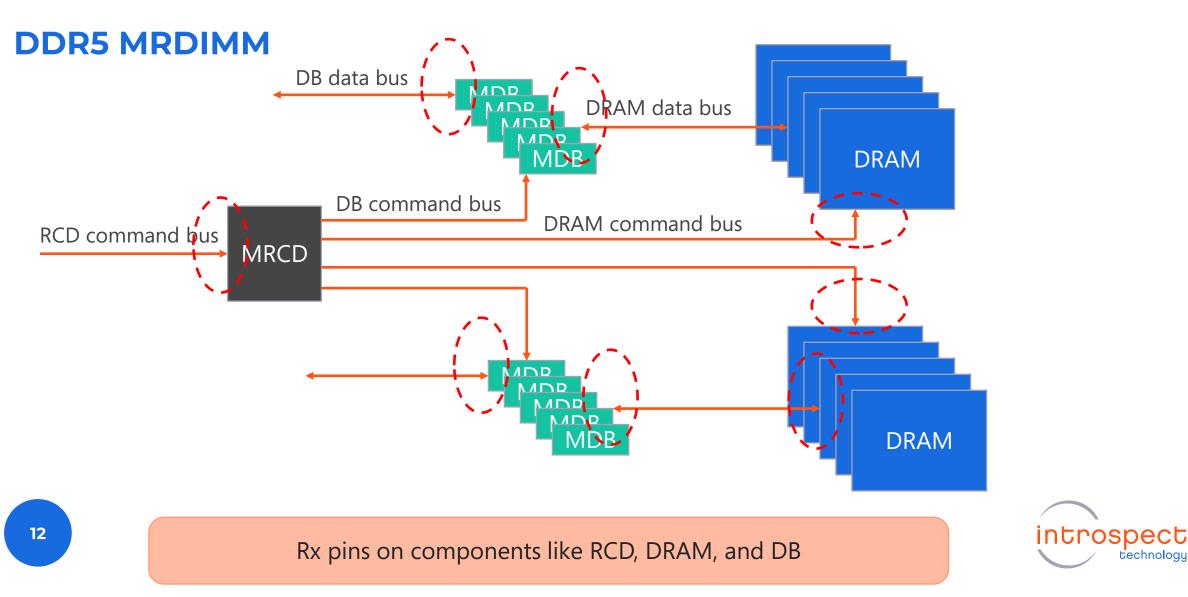

### Receiver Interfaces

### Validating Controller Components

Tx and Rx pins on memory controller devices

13

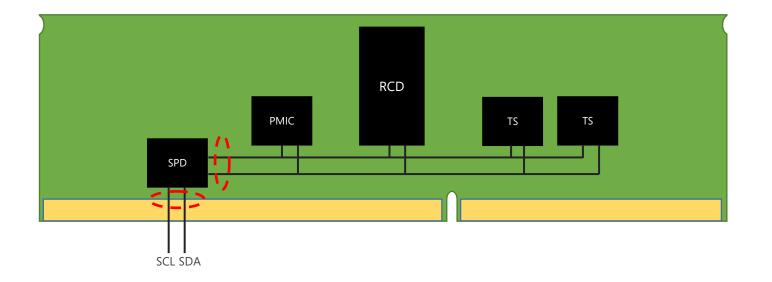

### Validating SidebandBus Components

All I2C/I3C interfaces on both the host bus and the local bus

14

# ATE on Bench Architecture

### Really Replace the ATE for DDR Testing

Complete training, shmooing capability on all pins

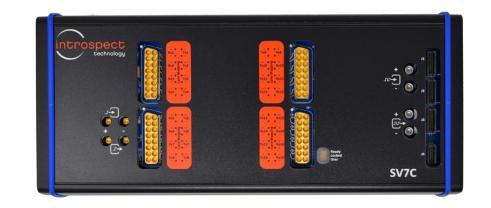

### SV7C-17 ATE on Bench Developed for ddr/lpddr/gddr interface testing

### ATE on Bench

#### **DEVELOPED FOR DDR/LPDDR/GDDR INTERFACE TESTING**

#### CAPTURE AND ANALYSIS

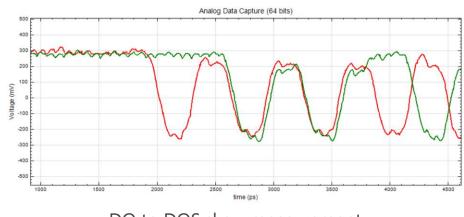

Eye diagrams and BER Parallel digital capture Analog capture

#### **16 RX CHANNELS**

Per lane phase contro Per lane voltage threshold

#### 16 ALIGNED RECEIVERS

capable of measuring tx skew

#### **AUXILIARY GPIO**

Provides a host ofsecondary controls (e.g. triggers, flags)

#### **16 TX CHANNELS**

\_\_\_+ ∿-} ⊙

+ (0) " []-+ (0)

SV7C

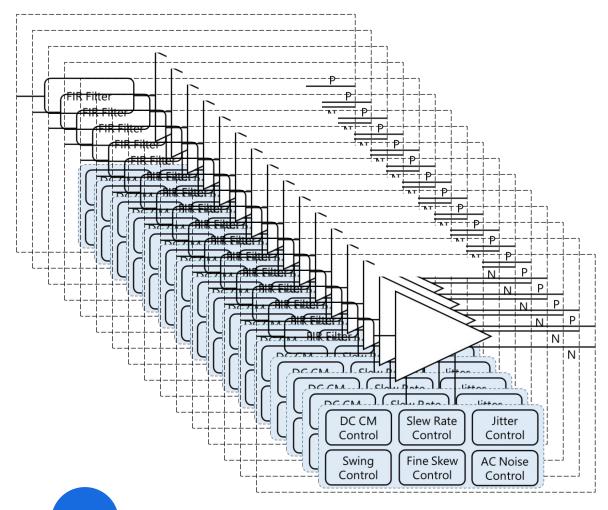

Per lane jitter and noise injection Per lane slew rate settings Per lane skew control Per lane voltage control

#### 16 PATTERN GENERATORS

Aligned on power up Protocol-configurable

### ATE on Bench

#### **DEVELOPED FOR DDR/LPDDR/GDDR INTERFACE TESTING**

#### CAPTURE AND ANALYSIS

Eye diagrams and BER Parallel digital capture Analog capture

#### **16 RX CHANNELS**

Per lane phase control Per lane voltage threshold

#### 16 ALIGNED RECEIVERS

capable of measuring tx skew

#### **AUXILIARY GPIO**

Provides a host of

secondary controls (e.g. triggers, flags)

#### **16 TX CHANNELS**

\_\_\_+ ∿-} ⊙

SV7C

Per lane jitter and noise injection Per lane slew rate settings Per lane skew control Per lane voltage control

#### 16 PATTERN GENERATORS

Aligned on power up Protocol-configurable

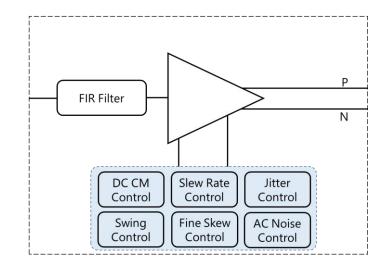

### Single-Lane Pin Electronic Driver

Clock Synthesizer

### All Drivers Work as a Bus

introspect technology

Can produce realistic DDR/LPDDR waveform shapes & skews

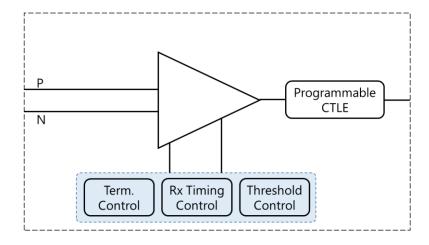

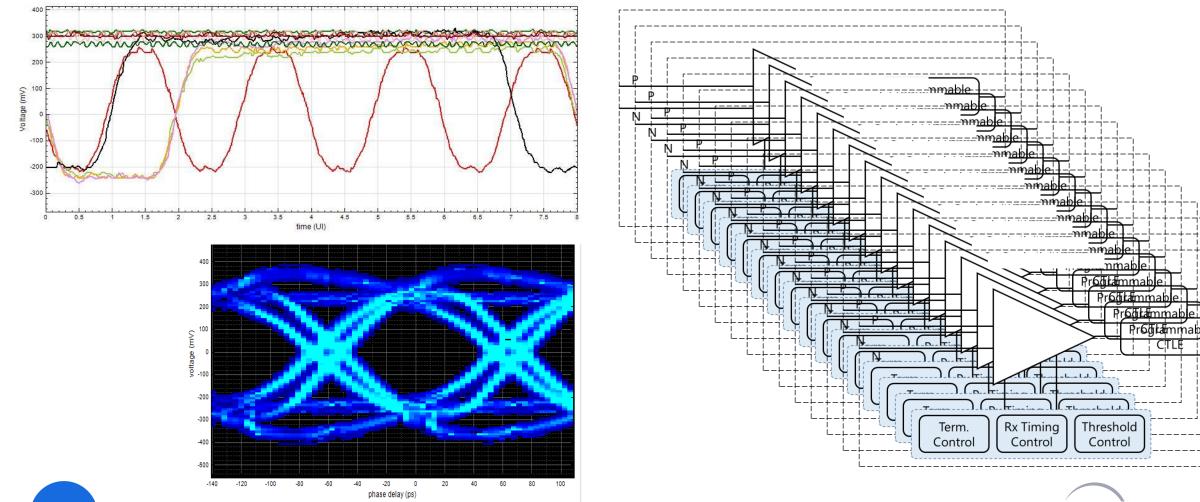

### Single-Lane Pin Electronic Receiver

22

### All Receivers Work as a Bus

Can capture complete bus behavior (digital and analog)

introspect

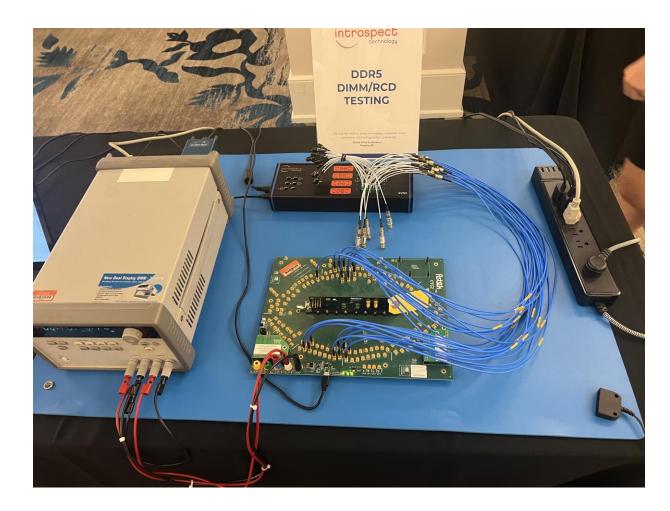

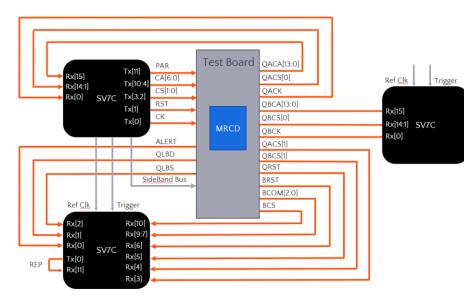

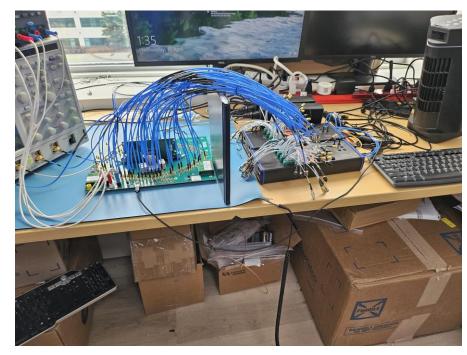

# Size Illustration (DDR and GDDR Component or PHY Test)

### Typical DDR5 Test Benches

DRAM

#### MRCD/RCD

#### CONTROLLER

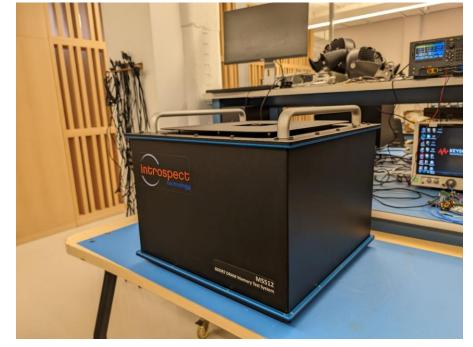

### Evolution to HS Memory ATE – M Series

DDR5 RDIMM Setup

Enclosed System to Hide the Cables and Increase Performance

### M Series Variants

#### **COMPONENT TESTER**

World-first PAM3 interop test on February 7, 2024 (with leading memory maker)

#### **COMPONENT TESTER**

**MODULE TESTER**

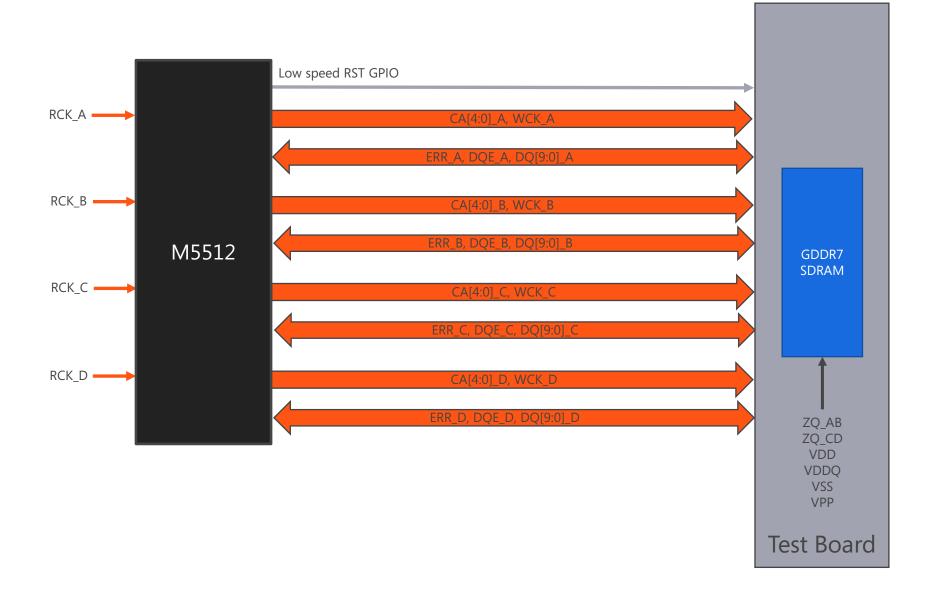

### Example: GDDR7 4-Channel System

introspect technology

28

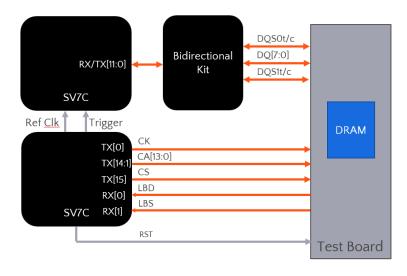

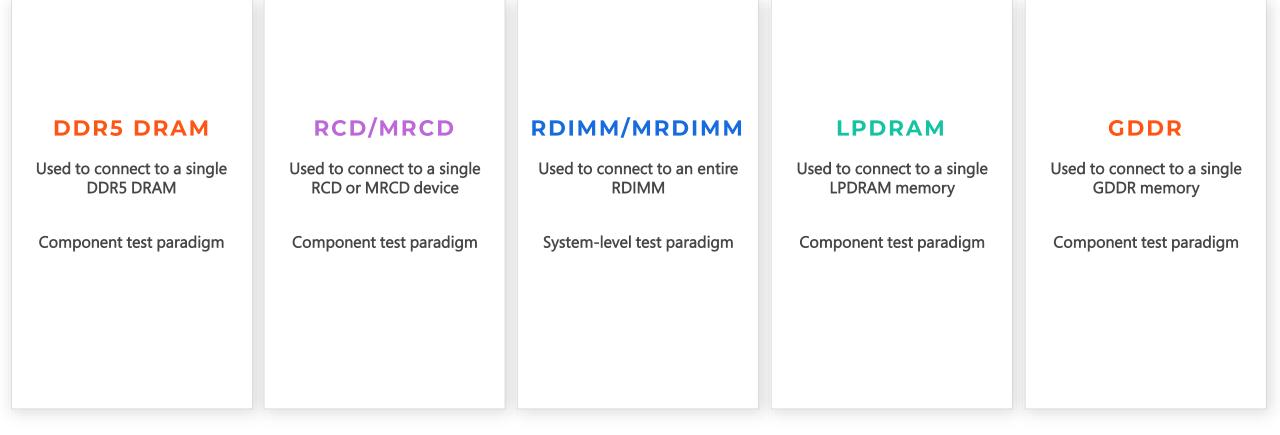

# Memory and Component Testing

### Memory Device Testing

#### **PHY LEVEL TESTING**

Adjustable voltage and timing parameters on all pins (including jitter injection)

#### **FUNCTIONAL TESTING**

Protocol-compliant stimulus for all memory commands

#### **FUNCTIONAL STRESS TESTING**

What are the limits of the device? Verify functional behaviour while pushing command timings, data rate and other parameters out of spec

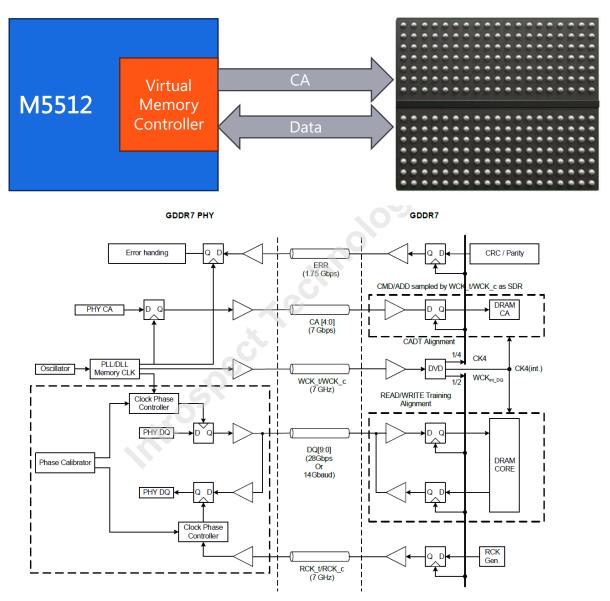

### Memory Controller Software (GD7 Example)

| ⊥ <br>⊺ ⊕  |  |

|------------|--|

| $\bigcirc$ |  |

<mark>∔†‡</mark> DramPhyParams

$\vee$  DDR

- 🚕 LpDramController

- ¦¦¦ LpDramParams

🛷 DramController

+++ DramParams

- **¦**¦¦ LpPhyParams

- <mark>∔¦</mark>+ PhyParams

- 希 RcdController

- ¦†¦ RcdParams

- 📌 RdimmController

- 🚕 GddrController

- ∔†‡ GddrParams

- <mark>∔</mark>†↓ GddrPhyParams

- <sup>∩100</sup> DdrDataCapture

- E DdrDbCommandPa...

- 📃 DdrDramCommand...

| Components |

|------------|

|------------|

gddrChannelLabeling1

📌 gddrController1

+++ gddrPhyParams1

pam3Protocol

+++ gddrParams1

#### gddrController1

÷.

|  | deviceSerialNum               | 1234                 |              |

|--|-------------------------------|----------------------|--------------|

|  | trainingDataFolderPath        |                      |              |

|  | memBusesUnderTest             | ABCD                 | $\checkmark$ |

|  | phyParams                     | gddrPhyParams1       | $\checkmark$ |

|  | gddrParams                    | gddrParams1          | $\checkmark$ |

|  | rxChannelLabeling             | gddrChannelLabeling1 | $\checkmark$ |

|  | txChannelLabeling             | gddrChannelLabeling1 | $\checkmark$ |

|  | calibrateZq                   | True                 | $\sim$       |

|  | trainingDataCaPhase           | auto                 | $\checkmark$ |

|  | caPhaseTrainingNumStepsPerUi  | 32                   |              |

|  | trainingDataCaVref            | auto                 | $\checkmark$ |

|  | caVrefTrainingStepSize        | 1                    |              |

|  | trainingDataReadVref          | auto                 | $\checkmark$ |

|  | trainingDataReadPam3EyeOffset | auto                 | $\checkmark$ |

|  | trainingDataReadPhase         | auto                 | $\checkmark$ |

|  |                               |                      |              |

#### Procedure

2

<

1 gddrController1.run()

- 3 #Sending MRS command...

- 4 gddrController1.sendMrs(13,128)

### Memory Controller Software (GD7 Example)

| ⊥ <br>⊺ ⊕ |  |

|-----------|--|

| (D        |  |

C

$\vee$  DDR

+++ DramPhyParams 🛹 LpDramController

🛷 DramController

+++ DramParams

- +++ LpDramParams

- +++ LpPhyParams

- +++ PhyParams

- ✤ RcdController

- +++ RcdParams

- RdimmController

- 📌 GddrController

- +++ GddrParams

- +++ GddrPhyParams

- 0100 DdrDataCapture

- DdrDbCommandPa...

- E DdrDramCommand...

Components

gddrChannelLabeling1

📌 gddrController1

+++ gddrPhyParams1

pam3Protocol

+++ gddrParams1

÷.

#### gddrController1

1234 deviceSerialNum trainingDataFolderPath memBusesUnderTest ABCD phyParams gddrPhyParams1 gddrParams gddrParams1 rxChannelLabeling gddrChannelLabeling1 txChannelLabeling gddrChannelLabeling1  $\sim$ calibrateZq  $\checkmark$ True trainingDataCaPhase  $\checkmark$ auto caPhaseTrainingNumStepsPerUi 32 trainingDataCaVref auto caVrefTrainingStepSize 1 trainingDataReadVref auto trainingDataReadPam3EyeOffset auto  $\checkmark$ trainingDataReadPhase auto

$\checkmark$

|          | gddrPhyParams1     |         |

|----------|--------------------|---------|

| _        | dataRate           | 16000.0 |

| Pro      | caVLow             | 250.0   |

| gd       | dqVLow             | 250.0   |

| #S<br>gd | wckVLow            | 200.0   |

|          | caVHigh            | 650.0   |

| gu       | dqVHigh            | 650.0   |

|          | rxVrefInitialValue | 600.0   |

|          | wckVHigh           | 600.0   |

|          |                    |         |

| gddrParams1            | <            |

|------------------------|--------------|

| readLatency            | 19           |

| writeLatency           | 10           |

| writeCrc               | False 🗸      |

| readCrc                | False 🗸      |

| cabi                   | False 🗸      |

| vrefDqlInitialValue    | 100          |

| vrefDqhInitialValue    | 100          |

| wrCrc2Err              | 10           |

| dqeRL                  | 1            |

| dqDqeRckDriverStrength | term400hm 🗸  |

| dqDqeTermination       | termOff 🗸    |

| errDriverStrength      | term400hm 🗸  |

| calUpd                 | allEnabled 🗸 |

| sev2Err                | False 🗸      |

| dqeHighZ               | False 🗸      |

### Driver Performance – 32 Gbps

### Pattern Generation Architecture

HOLD PATTERNS DRIVE IDLE STATES IN BETWEEN PATTERN SEQUENCES

busPatternTimeline.addPatterns(burstPattern,1)

busPatternTimeline.endWithPattern('HoldPattern')

busPatternTimeline.addPatterns(burstPattern1,1)

busPatternTimeline.addPatterns(idlePattern,1)

busPatternTimeline.addPatterns(burstPattern2,1)

busPatternTimeline.endWithPattern('HoldPattern')

### Pattern Generation Architecture

#### **IN BETWEEN PATTERN SEQUENCES...**

Start jitter injection on WCK...

Modify signal voltages levels on CA...

Control timings between DQ signals...

Change slew rate on DQ signals...

### Tuned Virtual Memory Controllers

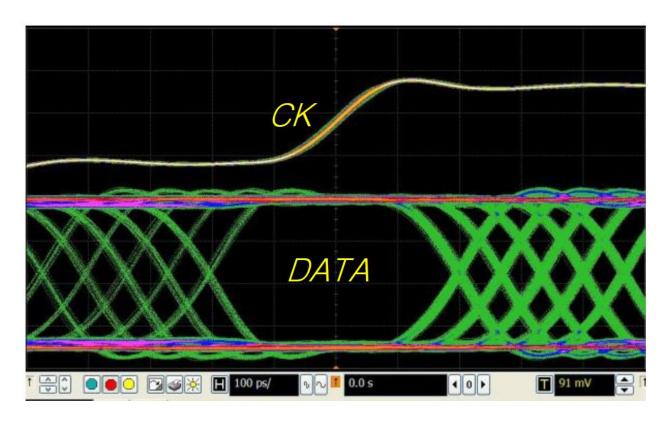

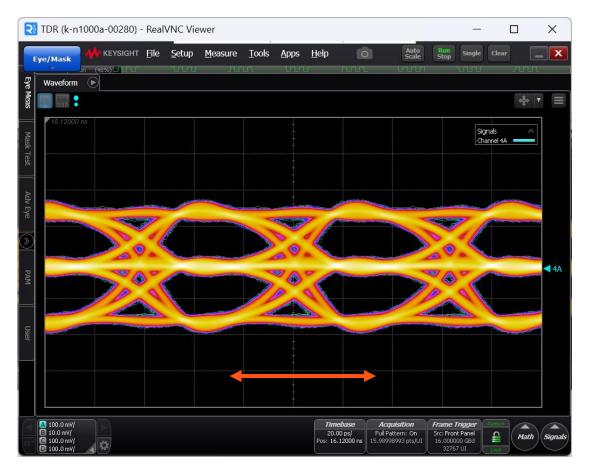

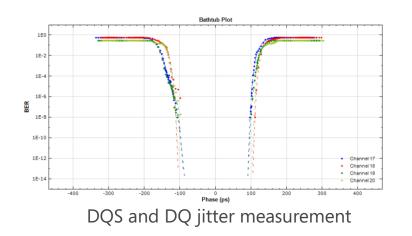

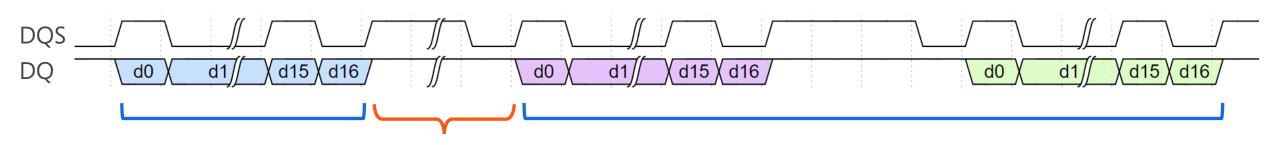

## Transmitter Characterization

- Clock to data skew measurement

- DQS to DQ

- CK to CA

- BCK to BCOM

- BERT measurements on clock and data

- Long duration error rate tests

- Eye diagrams

- Jitter measurements

- Slew rate measurements

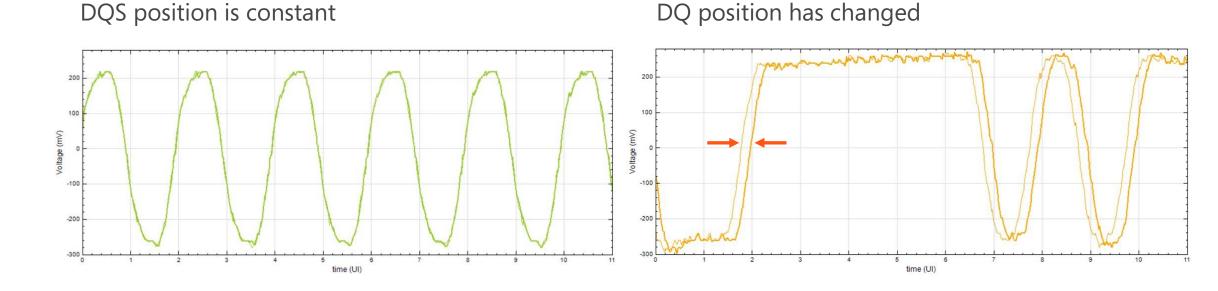

DQ to DQS skew measurement

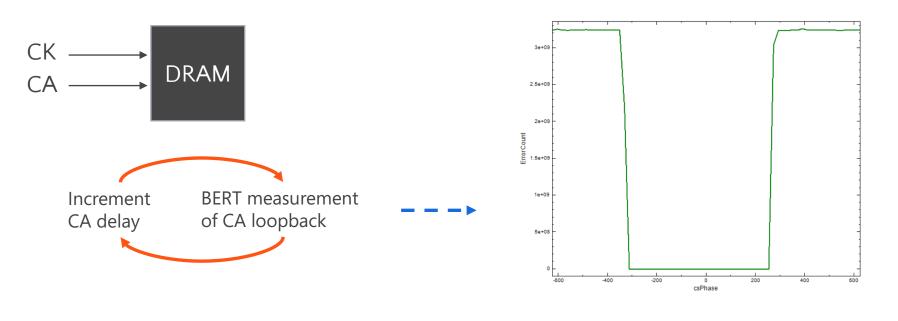

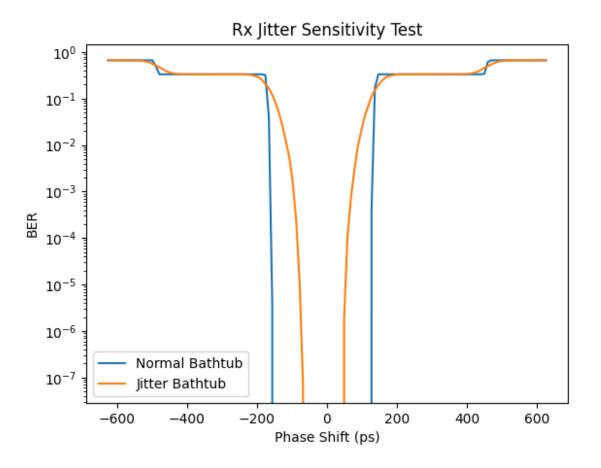

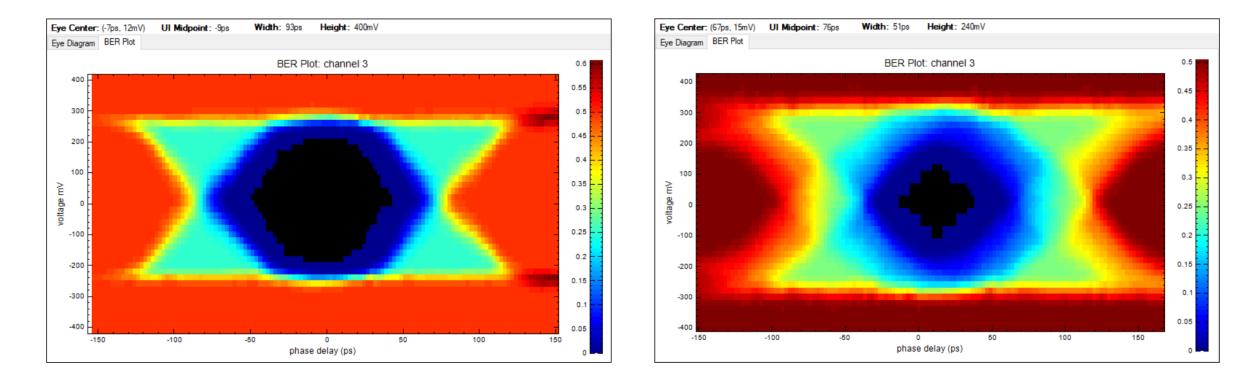

### **Receiver Characterization**

- Requires support of different loopback/training modes or uses write and read commands

- Measure horizontal and vertical eye opening at receiver while applying different stressors

- Jitter sensitivity clock to data skew

- Voltage sensitivity

- Stressed eye

### Example Receiver Stress Test Result

## Functional Testing

- Perform pass/fail checks of device behaviour under normal test conditions

- There is a wide variety of tests in this category, that can be roughly categorized as follows

- Functional mode tests E.g. Training modes, power down, DDR/SDR operation

- Input spec checks E.g. Mode register writes, MPC commands

- Output spec checks E.g. QCS operation, output inversion, Qx output delay

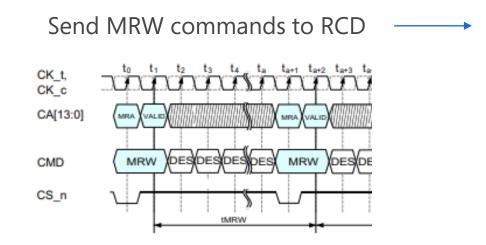

### **MODE REGISTER WRITE TEST EXAMPLE**

Read RW contents over sideband busPASS if read and write data matchFAIL if no match

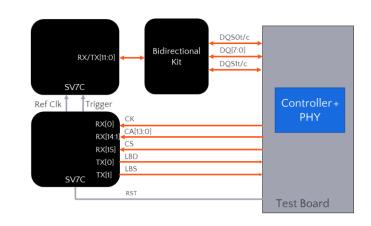

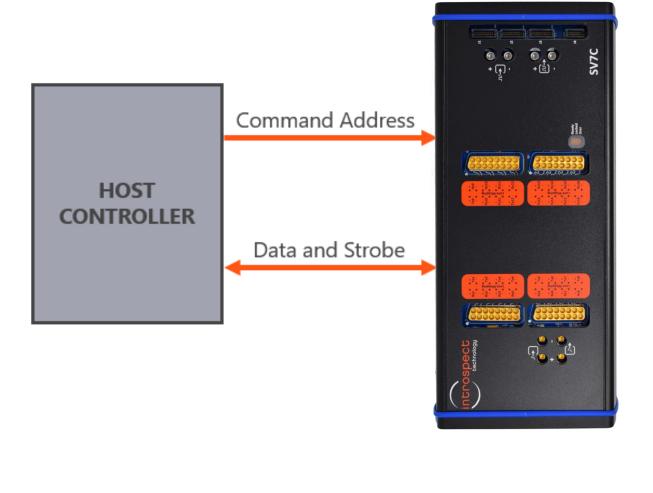

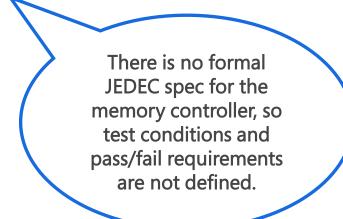

## Host Controller Testing

## **Controller** Testing

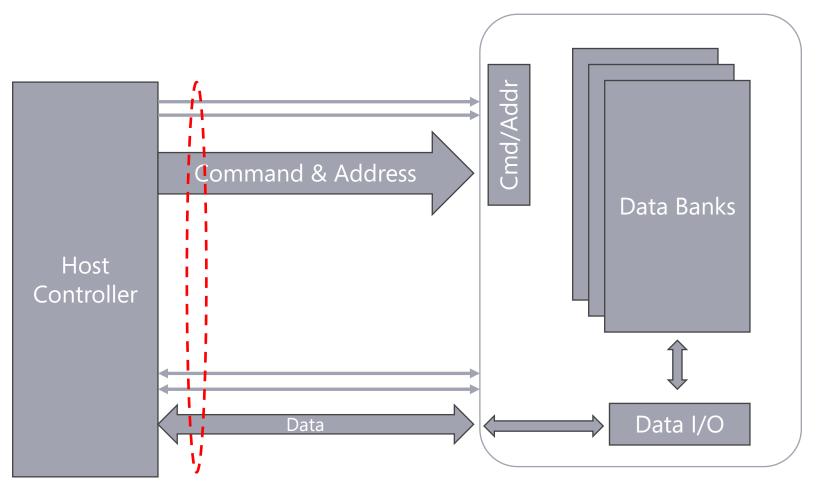

- Supports TX testing of command and data bus

- Clock to data skew measurements

- Eye diagrams, BER measurements etc...

- Supports RX testing of data bus using flexible pattern features and analog impairment controls. Requires loopback outputs, built-in error counters, or similar test mode in the host controller.

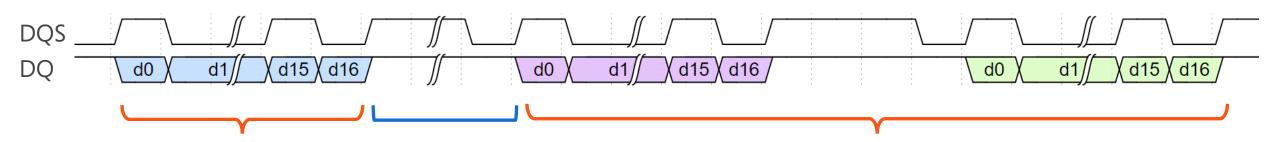

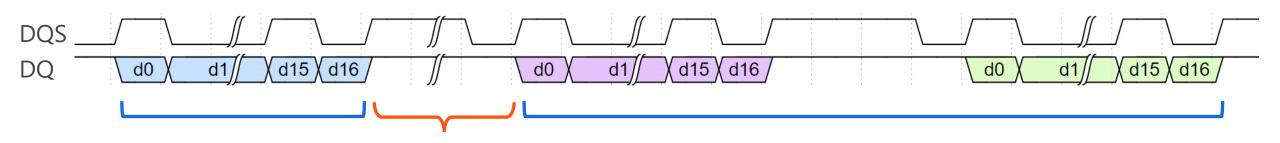

### Pattern Generation

### HOLD PATTERNS DRIVE IDLE STATES IN BETWEEN PATTERN SEQUENCES

busPatternTimeline.addPatterns(burstPattern,1)

busPatternTimeline.endWithPattern('HoldPattern')

busPatternTimeline.addPatterns(burstPattern1,1)

busPatternTimeline.addPatterns(idlePattern,1)

busPatternTimeline.addPatterns(burstPattern2,1)

busPatternTimeline.endWithPattern('HoldPattern')

### Pattern Generation

### **IN BETWEEN PATTERN SEQUENCES...**

Start jitter injection

Modify signal voltages levels

Control timings between signals

Change slew rate

## Timing and Voltage Control

### PER LANE PHASE, AMPLITUDE AND COMMON MODE SETTINGS

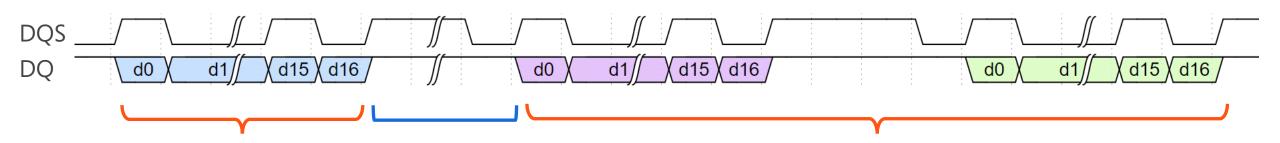

### Transmitter Skew Measurement

### **MEASURE CHANNEL TO CHANNEL SKEW**

Detect and measure DQ to DQS delay

### Transmitter Skew Measurement

### **VIEW PATTERN ALIGNMENT ON A SINGLE CHANNEL OVER TIME**

### **BERT** Measurements

Eye diagrams across different transmitter slew rate settings

## Burst Mode Digital Capture

### **CAPTURE AND FILTER OUT BURST DATA**

| Channel | Burst# | Offset | Status | Bits             |

|---------|--------|--------|--------|------------------|

| 1       |        |        |        |                  |

|         | 0      | 2      | good   | 10101010101010   |

|         | 1      | 66     | good   | 10101010101010   |

|         | 2      | 130    | good   | 10101010101010   |

|         | 3      | 194    | good   | 10101010101010   |

|         | 4      | 258    | good   | 10101010101010   |

| 2       |        |        |        |                  |

|         | 0      | 2      | good   | 0111011000110000 |

|         | 1      | 66     | good   | 0101000010100100 |

|         | 2      | 130    | good   | 0011001010110100 |

|         | 3      | 194    | good   | 0111011000110000 |

|         | 4      | 258    | good   | 0101000010100100 |

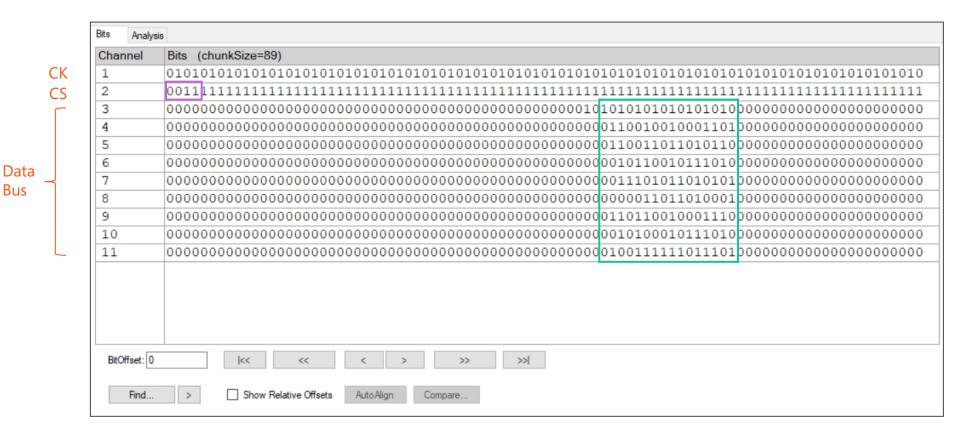

## Triggered Digital Capture

### **ONE-SHOT TRIGGER ON COMMAND AND CAPTURE DATA BUS IN PARALLEL**

## Continuously Triggered Capture

### **KEEP TRIGGERING ON COMMANDS (PROTOCOL ANALYZER)**

### **Receiver Characterization**

- Requires support of checking errors within the memory controller component

- Measure horizontal and vertical eye opening at receiver while applying different stressors

- Jitter sensitivity clock to data skew

- Voltage sensitivity

- Stressed eye

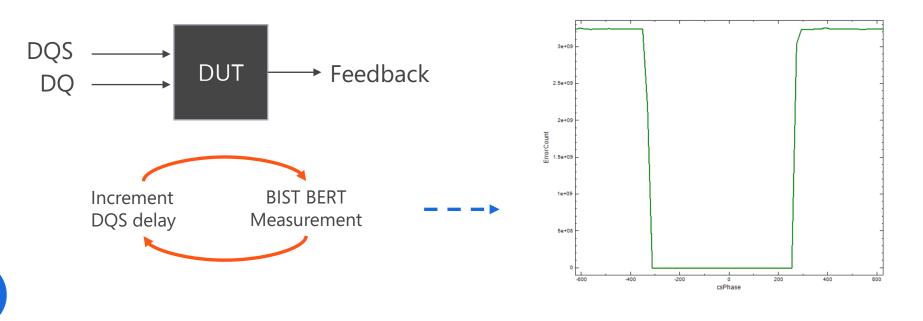

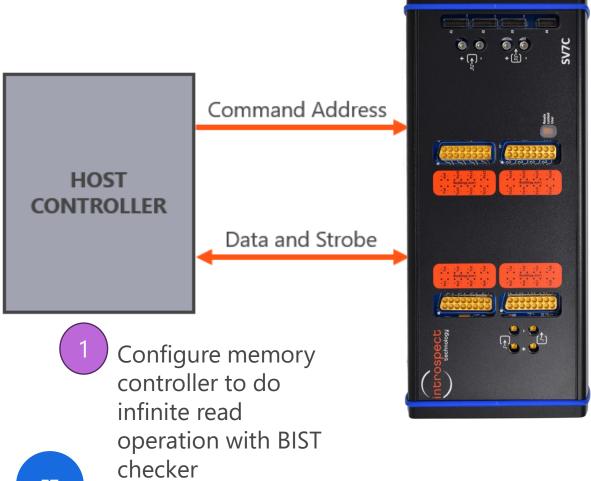

## Receiver Characterization Using BIST

- Two-step receiver characterization based on memory controller BIST mode

- In the first step, the BIST is enabled to perform infinite write/read operations or infinite read operations

- In the second step, the SV7C is programmed in Python to prepare the read response data and then transmit it

Pre-program read responses and read timings inside SV7C-17 and send the data with impairments

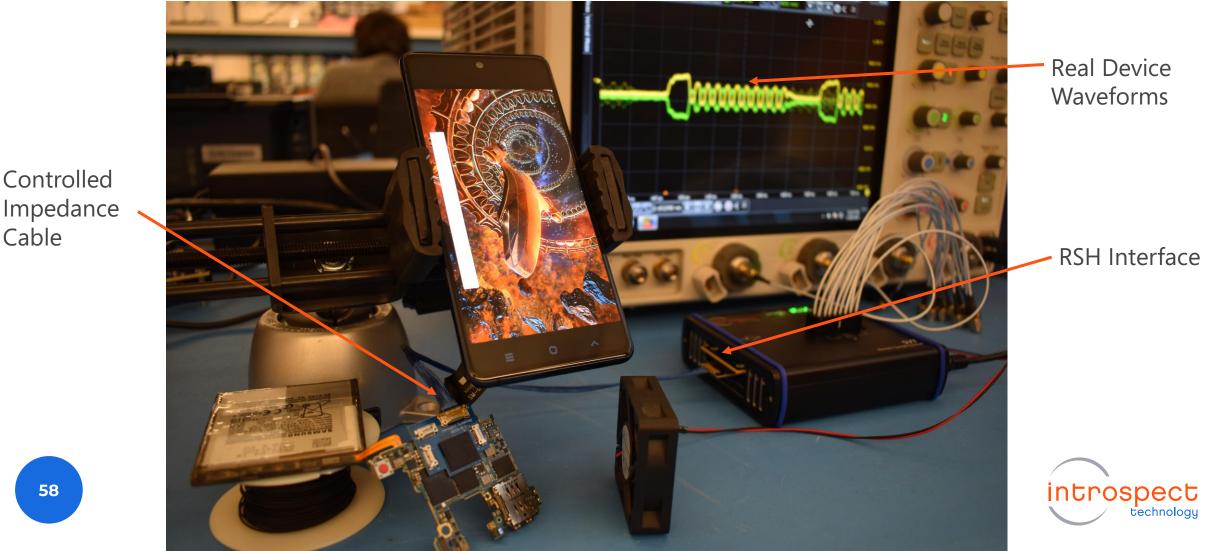

# Protocol Analyzer + Interposer Systems

# DDR5/LPDDR5 Protocol Analyzer

Same exerciser hardware but with a license for protocol analyzer

SV7

Heads (Up to 32 Channels)

**Remote Sampling**

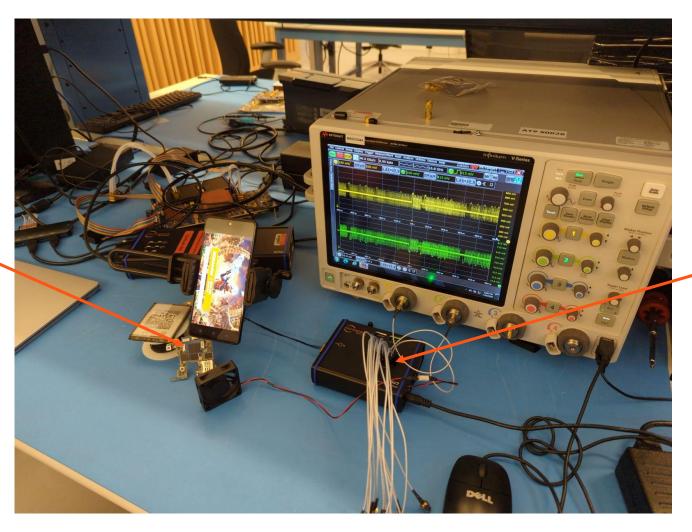

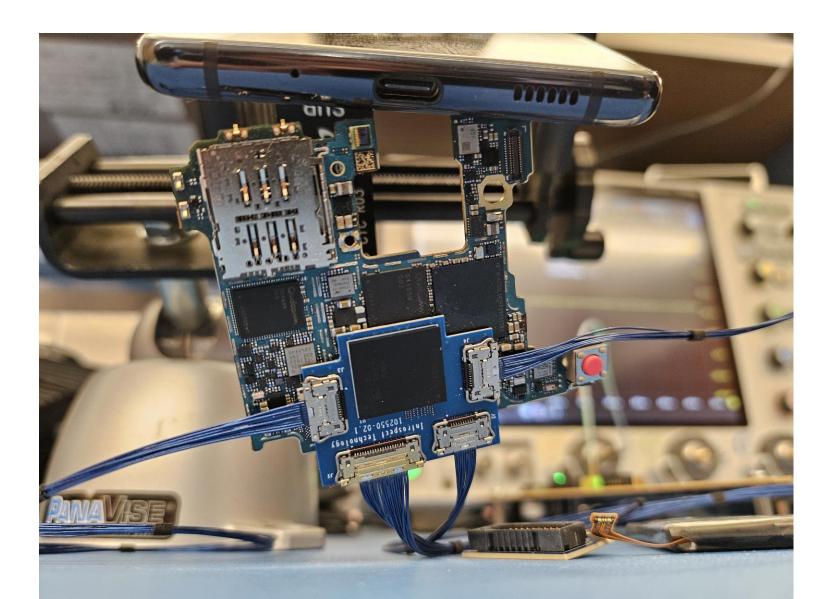

# DDR5/LPDDR5 Protocol Analyzer

Interposer system (example shown is PoP LPDDR5)

Remote Sampling Head (multi-channel <u>active probe</u>) connected to oscilloscope

### Zoomed View With All Pins Probed

### Probed Waveform Visible on Scope

Impedance Cable

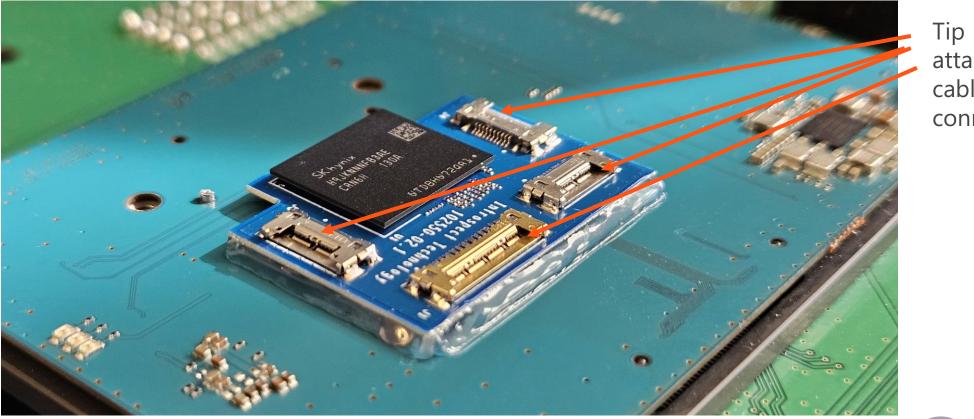

### Example Evaluation Board

Tip attachment cable connectors

### DDR5/LPDDR5 Protocol Analyzer FULL PROTOCOL ANALYSIS

| (                                                                        | Open Result F | Folder            |                      | ] |                 |                                          |             |                                          | 1                                                            |                                                                |                                                  |    |      |   |  |

|--------------------------------------------------------------------------|---------------|-------------------|----------------------|---|-----------------|------------------------------------------|-------------|------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------|----|------|---|--|

| Command Selecti                                                          | on            |                   |                      | 1 |                 | Command#                                 |             | Burst#                                   | 1.071                                                        | Name                                                           | BA                                               | BG | С    |   |  |

| Go To: Prev                                                              | Next Co       | mmand#            | ~                    |   |                 | 0                                        | 8           |                                          | ACT1<br>MRR                                                  |                                                                | A                                                |    |      |   |  |

|                                                                          | Next CO       | mmanu#            | ~                    |   |                 | 2                                        | 88          |                                          | ACT2                                                         |                                                                |                                                  |    |      |   |  |

| Command #2: De                                                           | ails          |                   |                      |   |                 | 3                                        | 256         |                                          | ACT2                                                         |                                                                | 8                                                |    |      |   |  |

| ame: ACTIVATE-                                                           | 2             |                   |                      |   |                 | 4                                        | 280         |                                          | ACT2                                                         |                                                                | , i i i i i i i i i i i i i i i i i i i          |    |      |   |  |

| Bits:                                                                    | Argur         |                   | Value                |   |                 | 5                                        | 384         |                                          | RD                                                           |                                                                | A                                                |    | 15   |   |  |

| CS CA23456                                                               |               | 12                |                      |   |                 | 6                                        | 408         |                                          | PRE                                                          |                                                                | А                                                |    |      |   |  |

| 11 1100000                                                               |               |                   |                      |   |                 | 7                                        | 416         |                                          | RD                                                           |                                                                | 8                                                |    | 15   |   |  |

| 1 0101000                                                                |               |                   |                      |   |                 | 🛛 Help: Timing                           | Definitions |                                          |                                                              |                                                                |                                                  |    |      | × |  |

| 4 (ACT2) 48.0 10.0 -<br>5 (RD) 74.0 36.0 -<br>6 (PRE) 80.0 84.0 1.40e+05 |               | nCK<br>nCK<br>nCK | tRRD<br>tRCD<br>tRAS |   | Command #0: Tim | 3<br>ings<br>Value                       | Min         | 256<br>Max Ur                            |                                                              | g Definitions                                                  |                                                  |    |      |   |  |

|                                                                          |               |                   |                      |   |                 |                                          | 2 (ACT2)    | 20.0                                     | -                                                            | 8.0 nCK                                                        |                                                  |    |      |   |  |

|                                                                          |               |                   |                      |   |                 | tAAD<br>tRRD<br>tRCD                     |             | 20.0<br>Delay be<br>Delay be<br>Delay be | -<br>etween AC<br>etween ACT                                 | 8.0 nCK<br>T2 and ACT1<br>T2 and ACT2 (dif<br>2 and any read/v | tAAD<br>Descriptio<br>ff. bank)<br>write/maskedW |    | nand |   |  |

|                                                                          |               |                   |                      |   |                 | tAAD<br>tRRD<br>tRCD<br>tRAS             | 2 (ACT2)    | 20.0<br>Delay be<br>Delay be<br>Delay be | tween AC<br>tween AC<br>twen ACT<br>tween ACT                | 8.0 nCK<br>T2 and ACT1<br>T2 and ACT2 (dif                     | tAAD<br>Descriptio<br>ff. bank)<br>write/maskedW |    | nand |   |  |

|                                                                          |               |                   |                      |   |                 | tAAD<br>tRRD<br>tRCD<br>tRAS<br>30       | 2 (ACT2)    | 20.0<br>Delay be<br>Delay be<br>Delay be | tween AC<br>tween AC<br>tween AC<br>tween AC<br>MRW1         | 8.0 nCK<br>T2 and ACT1<br>T2 and ACT2 (dif<br>2 and any read/v | tAAD<br>Descriptio<br>ff. bank)<br>write/maskedW |    | nand |   |  |

|                                                                          |               |                   |                      |   |                 | tAAD<br>tRRD<br>tRCD<br>tRAS<br>30<br>31 | 2 (ACT2)    | 20.0<br>Delay be<br>Delay be<br>Delay be | tween AC<br>tween AC<br>tween AC<br>tween AC<br>MRW1<br>MRW2 | 8.0 nCK<br>T2 and ACT1<br>T2 and ACT2 (dif<br>2 and any read/v | tAAD<br>Descriptio<br>ff. bank)<br>write/maskedW |    | nand |   |  |

|                                                                          |               |                   |                      |   |                 | tAAD<br>tRRD<br>tRCD<br>tRAS<br>30       | 2 (ACT2)    | 20.0<br>Delay be<br>Delay be<br>Delay be | tween AC<br>tween AC<br>tween AC<br>tween AC<br>MRW1         | 8.0 nCK<br>T2 and ACT1<br>T2 and ACT2 (dif<br>2 and any read/v | tAAD<br>Descriptio<br>ff. bank)<br>write/maskedW |    | nand |   |  |

introspect technology

## SV6E-X SidebandBus Controller and Tester

### **E SERIES**

### SV6E-X – I3C License

Mid-Frequency Digital Test Module

### **OVERVIEW**

Multi-Purpose Protocol Exerciser, Protocol analyzer, real-time oscilloscope Can be licensed for different mid-frequency digital protocols (I3C shown here)

### **FEATURES**

- Two banks of 10 channels each

- 200 MHz operating frequency

- Two programmable, high-current power supplies

- PurVue Analyzer<sup>TM</sup> technology on any channel

### **BENEFITS**

- Supports I3C, I3C Basic, JESD403, RCD, PMIC, SPD Hub, DMTF, MCTP

- Enables high-performance testing compared to other solutions

- Replaces racks of bench equipment

or PXI test systems

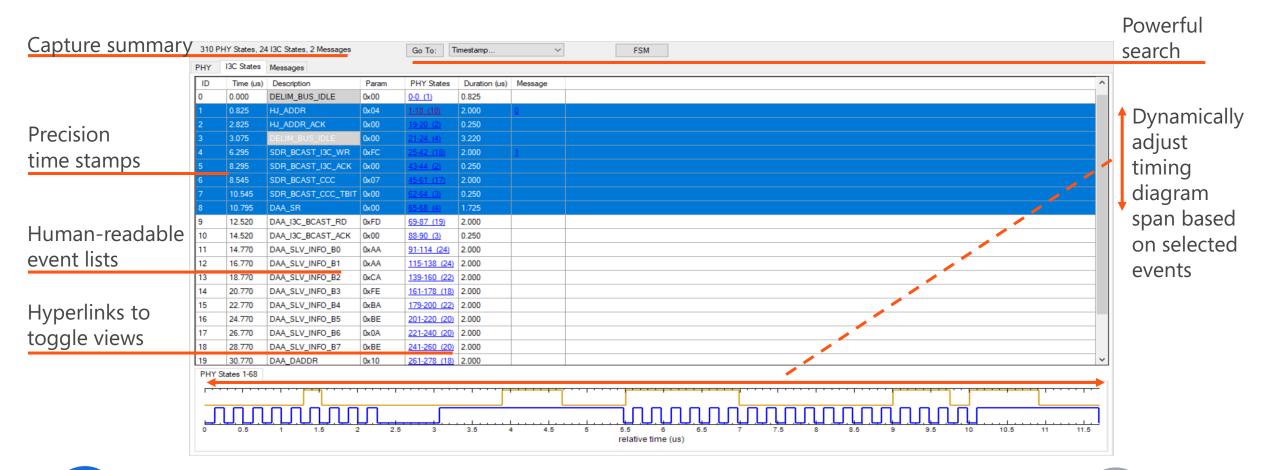

## Detailed Protocol Analyzer View

introspect

## Powerful Scripting and Logging

|                               | File Edit IESP/MIPI_I3C_EXERCISER Wizards ControlPanels Tools Results Help                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|                               | Params Log Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |

|                               | Resetting all dynamic addresses on bus<br>Assigning dynamic addresses<br>No dynamic addresses were assigned during DAA<br>Master DAA Table (0 entries)                                                                                                                                                                                                                                                                                                                                                 | ~ |

| Hot Join Example              | SUCCESS: Offline slave device successfully joined the bus                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |

|                               | 8<br>Reading Bus Characteristics Register for slvAddr=8<br>Bus 0 Master : Read BCR as [6] from slvAddr 8                                                                                                                                                                                                                                                                                                                                                                                               |   |

| liste way out Europeals       | SUCCESS: IBI request was acknowledged by the master                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

| Interrupt Example             | IBI regest was not acknowledged by the master                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

|                               | IBI reqest was not acknowledged by the master<br>IBI reqest was not acknowledged by the master |   |

|                               | Received the following interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |

| Mastership Request<br>Example | <pre>[{'interruptType': 'HJ', 'masterAcked': True, 'masterDisabledFuture': False}, {'interruptType': 'IBI', 'slaveAddr': 8, 'masterAcked': True, 'masterDisabledFuture': True, 'hasIbiPayload': False, 'ibiPayloadSize': 0, 'ibiPayload': None}] SUCCESS: Slave was able to become master</pre>                                                                                                                                                                                                        |   |

|                               | DAA Table (1 entries)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |

|                               | slvAddr=8, {'hasStaticAddr': False, 'provId': 1, 'bcr': 6, 'dcr': 0}<br>Test finished                                                                                                                                                                                                                                                                                                                                                                                                                  | ~ |

| 64                            | Run                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

### SidebandBus Controller Component

| Components                                                                                                                                                                                                                                               |                                                                                                      | sidebandBusController1 properties (class: SidebandBusController)                                                                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Components<br>i3cBus<br>i3cDataCapture<br><b>i3cProtocol</b><br>jedecSlaveDevice1<br>jedecSlaveDevice2<br>jedecSlaveDevice3<br>jedecSlaveParameters1<br>jedecSlaveParameters2<br>jedecSlaveParameters3<br>masterParams1<br><b>sidebandBusController1</b> | startup State<br>hid<br>auto Init Bus<br>pec Enabled<br>master Mode Params<br>bus<br>code For Config | sidebandBusController1 properties (class: SidebandBusController)          master       3         True       False         masterParams1       i3cBus         # Define some names for the slave addresses:dtisByName = { 'SPD': 0b1010, |

| Add Remove Config                                                                                                                                                                                                                                        |                                                                                                      | o "initializeBus" is part of "setup()" (and "update"). If "autoInitBus" is False, you will need to<br>Test procedure after the call to "setup()". If you are using a slave Device component as w                                       |

## Example of Set Bus Config

| _     |               | un_2021-03-26_1021 / i3c<br>I3C States, 42 Messages | DataCaptur  | e (i3cBus)          |               |          |     |

|-------|---------------|-----------------------------------------------------|-------------|---------------------|---------------|----------|-----|

| Go T  | To: Timestan  | ıp ~                                                | Times:      | relativeToStart     | ~             |          | FSM |

| PHY   | I3C States M  | essages                                             |             |                     |               |          |     |

| ID    | Time (us)     | Description                                         | Param       | PHY States          | Duration (us) | Message  | ^   |

| 27    | 499873.290    | DELIM_BUS_IDLE                                      | 0×00        | <u>298-310 (13)</u> | 599993.320    |          |     |

| 28    | 1099866.610   | SDR_BCAST_I3C_WR                                    | 0xFC        | <u>311-328 (18)</u> | 20.010        | <u>9</u> |     |

| 29    | 1099886.620   | SDR_BCAST_I3C_ACK                                   | 0×00        | <u>329-330 (2)</u>  | 2.500         |          |     |

| 30    | 1099889.120   | SDR_BCAST_CCC                                       | 0x0C        | <u>331-348 (18)</u> | 20.020        |          |     |

| 31    | 1099909.140   | SDR_BCAST_CCC_TBIT                                  | 0×01        | <u>349-351 (3)</u>  | 2.500         |          |     |

| 32    | 1099911.640   | SDR_BCAST_WR_DATA                                   | 0x80        | <u>352-368 (17)</u> | 20.010        |          |     |

| 33    | 1099931.650   | SDR_BCAST_WR_TBIT                                   | 0×00        | <u>369-370 (2)</u>  | 2.500         |          |     |

| 34    | 1099934.150   | DELIM_BUS_IDLE                                      | 0×00        | <u>371-374 (4)</u>  | 29996.820     |          | ~   |

| PHY S | tates 311-370 |                                                     |             |                     |               |          |     |

|       |               |                                                     | 30<br>relat | ive time (us)       | 40            |          |     |

### Example of SETHID

|        |               | un_2021-03-26_1021 / i3c | :DataCaptur | e (i3cBus)          |               |           |     |

|--------|---------------|--------------------------|-------------|---------------------|---------------|-----------|-----|

| Go T   |               |                          | Times:      | relativeToStart     | ~             |           | FSM |

| PHY    | I3C States M  | essages                  |             |                     |               |           |     |

| ID     | Time (us)     | Description              | Param       | PHY States          | Duration (us) | Message   | ^   |

| 41     | 1129998.510   | DELIM_BUS_IDLE           | 0x00        | 434-438 (5)         | 29913.890     |           |     |

| 42     | 1159912.400   | SDR_BCAST_I3C_WR         | 0xFC        | 439-456 (18)        | 20.010        | <u>11</u> |     |

| 43     | 1159932.410   | SDR_BCAST_I3C_ACK        | 0x00        | <u>457-458 (2)</u>  | 2.510         |           |     |

| 44     | 1159934.920   | SDR_BCAST_CCC            | 0x61        | <u>459-477 (19)</u> | 20.010        |           |     |

| 45     | 1159954.930   | SDR_BCAST_CCC_TBIT       | 0x00        | <u>478-480 (3)</u>  | 2.500         |           |     |

| 46     | 1159957.430   | SDR_BCAST_WR_DATA        | 0x06        | <u>481-498 (18)</u> | 20.010        |           |     |

| 47     | 1159977.440   | SDR_BCAST_WR_TBIT        | 0x01        | <u>499-501 (3)</u>  | 2.500         |           |     |

| 48     | 1159979.940   | DELIM_BUS_IDLE           | 0x00        | 502-506 (5)         | 39892.840     |           | ×   |

| PHY St | tates 439-501 |                          |             |                     |               |           |     |

|        |               |                          |             | ive time (us)       |               |           |     |

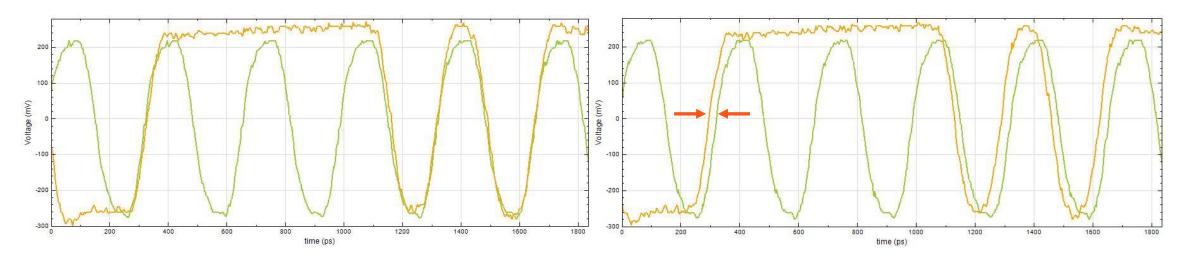

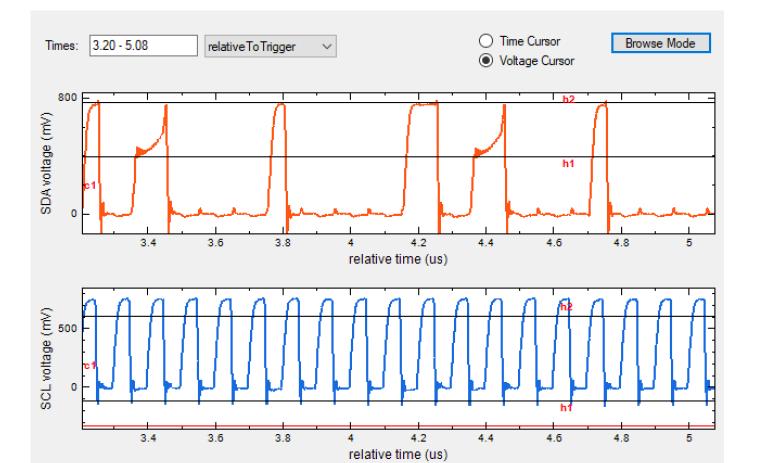

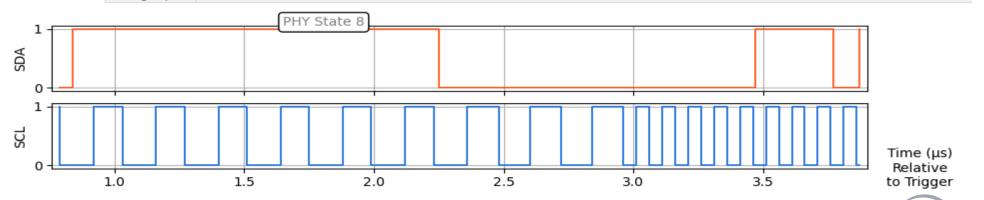

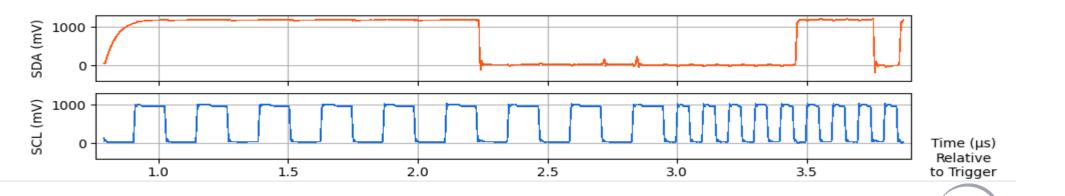

### Real-Time, Single-Shot View of Signals

- I3C PurVue Analyzer<sup>™</sup> embedded real-time oscilloscope license provides a real-time, single-shot view of all I3C signals

- It eliminates probing hassles with conventional scopes (attachment issues, cost issues, EMI issues) and completely eliminates the need for using a conventional scope

Pristine signal measurement is shown here where there are no artefacts due to the probes picking up noise from Wi-Fi or RF signals

### Why? Because Probes Are Antennas

Most oscilloscope probes result in too much noise pickup The SV4E oscilloscope is embedded into the I3C signal plane, so it has far less noise

69

introspect technology

## PurVue Analyzer<sup>TM</sup> Capture

- A single component for <u>simultaneous</u> protocol capture (digital capture) and oscilloscope capture (analog capture)

- Familiar user interface (the viewer is almost identical to the I3cDataCapture)

- With the PurVue viewer, users can quickly find interesting parts of the waveform since it is protocol-aware

|                     | i3cPurVueCapture1 properties (class: I3cPurVueCapture) |  |  |  |  |

|---------------------|--------------------------------------------------------|--|--|--|--|

| analogCapturePort   | 1                                                      |  |  |  |  |

| digitalCaptureBus   | i3cBus                                                 |  |  |  |  |

| triggerCondition    | privateRead                                            |  |  |  |  |

| preTriggerDuration  | 5000                                                   |  |  |  |  |

| postTriggerType     | numberOfFrames                                         |  |  |  |  |

| postTriggerDuration | 1                                                      |  |  |  |  |

| slaveAddrForTrigger | None                                                   |  |  |  |  |

| saveResults         | True                                                   |  |  |  |  |

## PurVue Analyzer<sup>TM</sup> Digital View

🔯 I3C PurVue Capture: Run\_2022-08-08\_1516 / i3cPurVueCapture1

– 🗆 🗙

introspect

technolog

274 PHY States, 21 I3C States, 1 Transactions

Times: RelativeToTrigger ~

PHY I3C States Transactions

| ID | Time (µs) | Description       | Param | PHY States       | Duration (µs) | Transaction | Info        |  |

|----|-----------|-------------------|-------|------------------|---------------|-------------|-------------|--|

| 0  | 0.000     | DELIM_BUS_FREE    | 0x00  | <u>0-0 (1)</u>   | 0.810         |             |             |  |

| 1  | 0.810     | SDR_BCAST_I3C_WR  | 0xFC  | <u>1-18 (18)</u> | 1.930         | <u>0</u>    |             |  |

| 2  | 2.740     | SDR_BCAST_I3C_ACK | 0x00  | <u>19-20 (2)</u> | 0.240         |             |             |  |

| 3  | 2.980     | SDR_CCC           | 0x07  | 21-38 (18)       | 0.800         |             | CCC: ENTDAA |  |

| 4  | 3.780     | SDR_CCC_TBIT      | 0x00  | <u>39-41 (3)</u> | 0.100         |             |             |  |

| 5  | 3.880     | DAA_SR            | 0x00  | 42-45 (4)        | 1.650         |             |             |  |

| 6  | 5.530     | DAA_I3C_BCAST_RD  | 0xFD  | 46-64 (19)       | 0.800         |             |             |  |

| 7  | 6.330     | DAA_I3C_BCAST_ACK | 0x00  | <u>65-66 (2)</u> | 0.240         |             |             |  |

| 8  | 6.570     | DAA_SLV_INFO_B0   | 0xCF  | 67-86 (20)       | 1.920         |             |             |  |

| 9  | 8.490     | DAA_SLV_INFO_B1   | 0x2A  | 87-108 (22)      | 1.920         |             |             |  |

#### Digital Capture (PHY States 1-41) Analog Capture

## PurVue Analyzer<sup>TM</sup> Analog View

I3C PurVue Capture: Run\_2022-08-08\_1516 / i3cPurVueCapture1

274 PHY States, 21 I3C States, 1 Transactions

Times: RelativeToTrigger ~

PHY I3C States Transactions

| ID | Time (µs) | Description       | Param | PHY States       | Duration (µs) | Transaction | Info        |  |

|----|-----------|-------------------|-------|------------------|---------------|-------------|-------------|--|

| 0  | 0.000     | DELIM_BUS_FREE    | 0x00  | 0-0 (1)          | 0.810         |             |             |  |

| 1  | 0.810     | SDR_BCAST_I3C_WR  | 0xFC  | <u>1-18 (18)</u> | 1.930         | <u>0</u>    |             |  |

| 2  | 2.740     | SDR_BCAST_I3C_ACK | 0x00  | <u>19-20 (2)</u> | 0.240         |             |             |  |

| 3  | 2.980     | SDR_CCC           | 0x07  | 21-38 (18)       | 0.800         |             | CCC: ENTDAA |  |

| 4  | 3.780     | SDR_CCC_TBIT      | 0x00  | <u>39-41 (3)</u> | 0.100         |             |             |  |

| 5  | 3.880     | DAA_SR            | 0x00  | 42-45 (4)        | 1.650         |             |             |  |

| 6  | 5.530     | DAA_I3C_BCAST_RD  | 0xFD  | 46-64 (19)       | 0.800         |             |             |  |

| 7  | 6.330     | DAA_I3C_BCAST_ACK | 0x00  | <u>65-66 (2)</u> | 0.240         |             |             |  |

| 8  | 6.570     | DAA_SLV_INFO_B0   | 0xCF  | 67-86 (20)       | 1.920         |             |             |  |

| 9  | 8.490     | DAA_SLV_INFO_B1   | 0x2A  | 87-108 (22)      | 1.920         |             |             |  |

$\times$

introspect

technologu

Digital Capture (PHY States 1-41) Analog Capture

72

### Summary

### **HIGHLY DIFFERENTIATED SOLUTIONS**

- Introspect develops parallel test instruments for high-speed interfaces

- We have created a rich portfolio of solutions for sourcesynchronous and DDR interfaces

- Our solutions can be deployed at the component level and at the module level