**DATA SHEET**

# SV3D09 Direct-Attach SerDes Module

**D SERIES**

# **Table of Contents**

| Table of Contents                                         | 2  |

|-----------------------------------------------------------|----|

| List of Figures                                           |    |

| List of Tables                                            |    |

| Introduction                                              |    |

|                                                           |    |

| Overview                                                  |    |

| Key Benefits                                              |    |

| Applications                                              |    |

| Features                                                  | 7  |

| Multi-Lane Loopback                                       | 7  |

| Multiple-Source Jitter Injection                          | 8  |

| Pre-Emphasis Generation                                   | 9  |

| Burst-Mode BER Testing                                    | 11 |

| Programmable SSC Generation and Frequency Synthesis       | 12 |

| Per-Lane Clock Recovery and Unique Dual-Path Architecture | 13 |

| Auxiliary Control Port                                    |    |

| Parallel Transfer Interface                               |    |

| Standard Error Detector Analysis                          |    |

| Automation                                                |    |

| Physical Description                                      |    |

| •                                                         |    |

| Loadboard Connectors Footprint and Dimensions             |    |

| Electrical Description                                    | 20 |

| Specifications                                            | 29 |

# List of Figures

| Figure 1   | Illustration of loopback applications                                               | 8     |

|------------|-------------------------------------------------------------------------------------|-------|

| Figure 2   | Illustration of calibrated jitter waveform                                          | 8     |

| Figure 3   | Illustration of jitter tolerance curve                                              | 9     |

| Figure 4   | Illustration of pre-emphasis design                                                 | .10   |

| Figure 5   | Illustration of multiple waveform shapes that can be synthesized using the pre-empl | nasis |

| function c | of the SV3D                                                                         | .10   |

| Figure 6   | Illustration of burst-mode error detection.                                         |       |

| Figure 7   | Programmable SSC generation                                                         | .12   |

| Figure 8   | Per-lane clock recovery and dual-path architecture                                  | .13   |

| Figure 9   | PTI clock / data relationship for 12.5 MHz (single data rate) operation             | .14   |

| _          | Sample waveform for 24 byte PTI transfer                                            |       |

| Figure 11  | Sampling of analysis and report windows                                             | .16   |

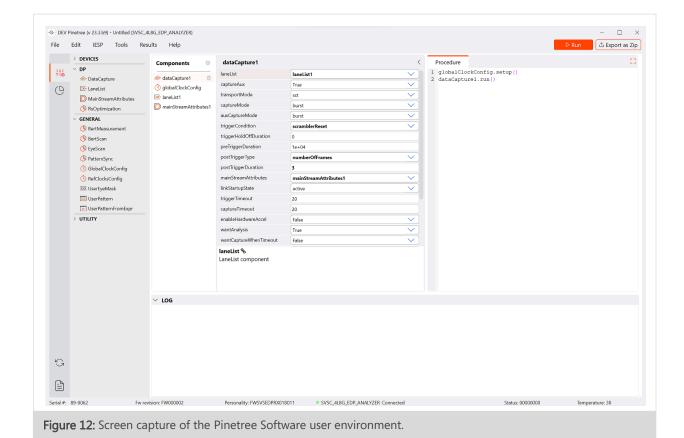

| Figure 12  | Screen capture of Pinetree user environment                                         | .17   |

| Figure 13  | Top view of SV3D module                                                             | .18   |

|            | Bottom view of SV3D module                                                          |       |

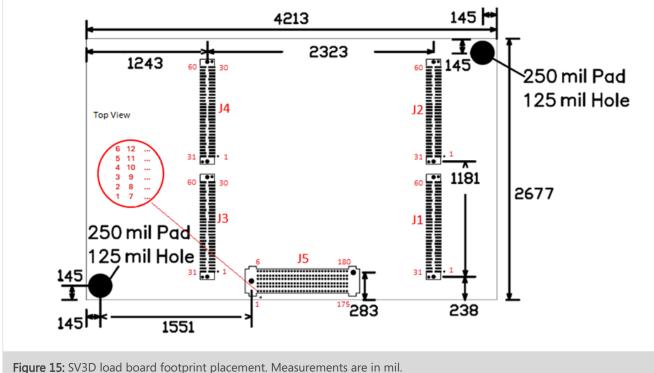

| Figure 15  | SV3D loadboard footprint placement. Measurements are in mil                         | .19   |

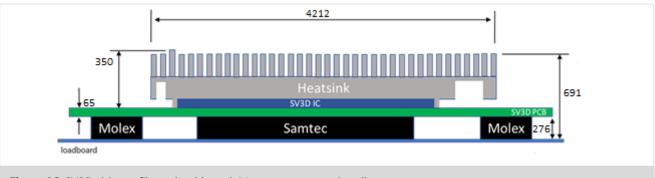

| Figure 16  | SV3D side profile on loadboard. Measurements are in mil                             | .19   |

# List of Tables

| Table 1  | Loadboard Connectors Descriptions | 20 |

|----------|-----------------------------------|----|

| Table 2  | Load board J1 Connector Pin-Out   | 20 |

| Table 3  | Load board J2 Connector Pin-Out   | 22 |

| Table 4  | Load board J3 Connector Pin-Out   | 23 |

| Table 5  | Load board J4 Connector Pin-Out   | 24 |

| Table 6  | Load Board J5 Connector Pin-Out*  | 25 |

| Table 7  | General Specifications            | 29 |

| Table 8  | Transmitter Characteristics       | 30 |

| Table 9  | Receiver Characteristics          | 33 |

| Table 10 | Clocking Characteristics          | 34 |

| Table 11 | Pattern Handling Characteristics  | 35 |

| Table 12 | Instruction Sequence Cache        | 36 |

| Table 13 | DUT Control Capabilities          | 36 |

## Introduction

#### **OVERVIEW**

The SV3D Direct-Attach SerDes Module is a versatile, high-performance instrument that creates a new category of tool for high-speed digital product engineering teams. It integrates multiple technologies to enable the self-contained test and measurement of SerDes interfaces such as PCI Express Gen 3, MIPI M-PHY or USB3 and advanced protocols such as MIPI C-PHY and MIPI D-PHY. The SV3D mounts directly on an application or test board without cables. It contains 32 independent SerDes stimulus generation ports, 24 independent capture and measurement SerDes ports and various clocking, synchronization, and lane-expansion capabilities. It has been designed specifically to address the growing need of a parallel, system-oriented test methodology while offering world-class signal-integrity features such as jitter injection and jitter measurement.

With a small footprint, an extensive signal-integrity feature set, and an exceptionally powerful software development environment, the SV3D is not only suitable for signal-integrity verification engineers that perform traditional characterization tasks, but it is also ideal for FPGA developers and software developers who need rapid turnaround signal verification tools or hardware-software interoperability confirmation tools. The SV3D integrates state of the art functions such as digital data capture, bit error rate measurement, clock recovery, jitter decomposition and jitter generation.

#### **KEY BENEFITS**

- True parallel bit-error-rate measurement across 24 RX lanes

- Fully synthesized integrated jitter injection on all 32 TX lanes

- Fully automated integrated jitter testing on all lanes

- Optimized pattern generator rise-time for receiver stress test applications

- Flexible pre-emphasis and equalization

- Flexible loopback support per lane

- Hardware clock recovery per lane

- State of the art programming environment based on the highly intuitive Python language

- Integrated device control through SPI, I2C, or JTAG

- Reconfigurable, protocol customization (on request)

- Reconfigurable GPIOs

- RoHS Compliant (meets 2011/65/EU RoHS Directive)

#### **APPLICATIONS**

Parallel PHY validation of serial bus standards such as:

PCI Express (PCIe)

HDMI

• UHS-2

Thunderbolt

MIPI M-PHY

XAUI

CPRI

JESD204B

USB

SATA

Interface test of electrical/optical media such as:

- Backplane

- Cable

- CFP MSA, SFP MSA, SFP+ MSA

Plug-and-play system-level validation such as:

- PCI Express

- MIPI D-PHY, CSI/DSI Protocols

- MIPI M-PHY, UniPro Protocols

### Timing verification:

- PLL transfer function measurement

- Clock recovery bandwidth verification

- Frequency ppm offset characterization

Mixed-technology applications:

- High-speed ADC and DAC (JESD204) data capture and/or synthesis

- FPGA-based system development

- Channel and device emulation

# **Features**

#### **MULTI-LANE LOOPBACK**

The SV3D is the only bench-top tool that offers instrument-grade loopback capability on differential lanes.\* The loopback capability of the SV3D includes:

- Retiming of data for the purpose of decoupling DUT receiver performance from DUT transmitter performance

- Arbitrary jitter or voltage swing control on loopback data

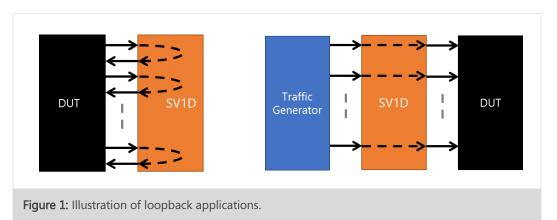

Figure 1 shows two common loopback configurations that can be used with the SV3D. In the first configuration, a single DUT's transmitter and receiver channels are connected through the SV3D. In the second configuration, arbitrary pattern testing can be performed on an end-to-end communications link. The SV3D is used to pass data through from a traffic generator (such as an endpoint on a real system board) to the DUT while stressing the DUT receiver with jitter, skew, or voltage swing.

SV3D09 Direct-Attach SerDes Module INTROSPECT.CA

<sup>\*</sup> The SV3D09 consists of 32 TX channels and 24 RX channels, for 24 loopback connections in total.

#### **MULTIPLE-SOURCE JITTER INJECTION**

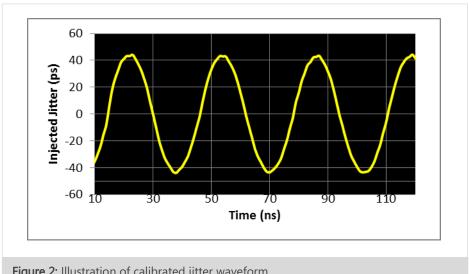

The SV3D can generate calibrated jitter stress on any data pattern and any output lane configuration. Sinusoidal jitter injection is calibrated in the time and frequency domain to generate high-purity stimulus signals as shown in Figure 2.

Figure 2: Illustration of calibrated jitter waveform.

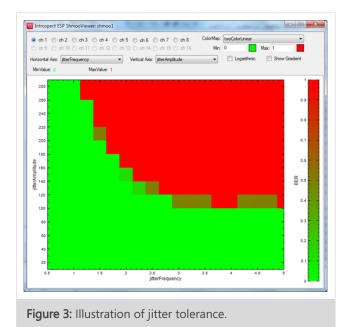

The jitter injection feature is typically exploited to perform automated jitter tolerance testing as shown in the example in Figure 3. As is the case for other features in the SV3D Direct-Attach SerDes Module, jitter tolerance testing is conducted in parallel across all lanes. For advanced applications, the SV3D also includes RJ injection and a third-source arbitrary waveform jitter synthesizer.

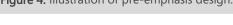

#### PRE-EMPHASIS GENERATION

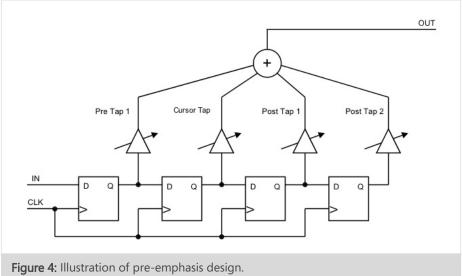

Conventionally offered as a separate instrument, per-lane pre-emphasis control is integrated on the 8-lane SV3D tester. The user can individually set the transmitter pre-emphasis using a built-in Tap structure. Pre-emphasis allows the user to optimize signal characteristics at the DUT input pins.

Each transmitter in the SV3D implements a discrete-time linear equalizer as part of the driver circuit. An illustration of such equalizer is shown in Figure 4, and sample synthesized waveform shapes are shown in Figure 5.

**Figure 5:** Illustration of multiple waveform shapes that can be synthesized using the pre-emphasis function of the SV3D.

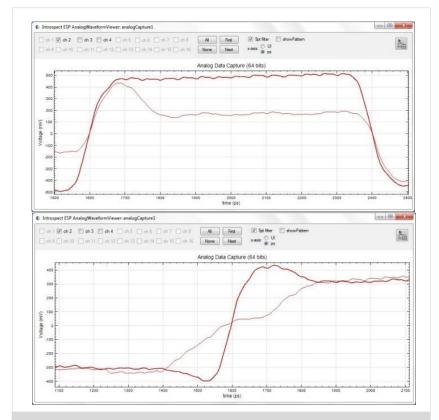

#### **BURST-MODE BER TESTING**

Modern SerDes interfaces require complex training sequences and sophisticated power-efficient operating modes. Often called burst-mode, many SerDes transmissions require a new class of Error Detector: one that can compute BER on only sections of a non-continuous transmitted data stream. The SV3D includes the optional ability to automatically track intermittent sleep/burst cycles within a test pattern and to measure only relevant payload sections. This is illustrated in Figure 6. In the figure, the link is asleep for a long time (indicated by the static low and static high levels), then some training "SYNC" pattern is transmitted for a short burst before payload data is transmitted. Once the payload data is transmitted, the SV3C automatically resumes error detection and error counting.

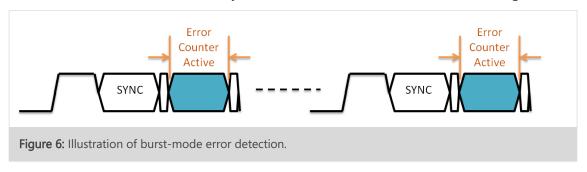

### PROGRAMMABLE SSC GENERATION AND FREQUENCY SYNTHESIS

The SV3D incorporates precision frequency synthesis technology that allows for the generation of programmable SSC waveforms at any data rate. The SSC waveforms are superimposed on the pattern generator outputs, and they coexist with other jitter injection sources of the SV3D. Thus, a truly complete jitter cocktail can be produced for the most thorough receiver validation. Figure 7 illustrates the SSC capability of the SV3D. In the figure, the SV3D is programmed to synthesize four slightly different modulation frequencies showcasing the precision programmability of the tool.

Figure 7: Programmable SSC Generation.

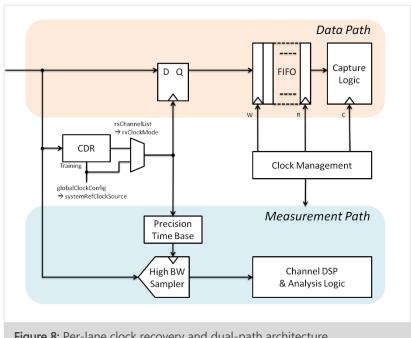

# PER-LANE CLOCK RECOVERY AND UNIQUE DUAL-PATH **ARCHITECTURE**

True to the integrated nature of its design, each SV3C receiver has its own embedded analog clock recovery circuit. That is, 24 individual CDR circuits are monolithically integrated in this miniature test system, thus offering the lowest possible sampling latency in a test and measurement instrument.

The monolithic nature of the SV3C clock recovery helps achieve wide tracking bandwidth for measuring signals that possess spread-spectrum clocking or very high amplitude wander.

Figure 8 shows a block diagram of the clock recovery capability inside the SV3C Personalized SerDes Tester. Also shown in Figure 8 is the dual-path receiver architecture of the SV3C. This unique architecture allows the SV3C to operate as both a digital capture/analysis instrument and an analog measurement instrument. A feature rich clock management system allows for customization of the SV3C to specific customer requirements.

Figure 8: Per-lane clock recovery and dual-path architecture.

#### **AUXILIARY CONTROL PORT**

The SV3D includes a low-speed auxiliary control port. It enables controlling DUT registers through JTAG, I2C, or SPI. Additionally, the port includes two reconfigurable trigger and five flag capabilities for synchronizing with external tools or events. The pin location for these controls are as given in Table 6.

#### PARALLEL TRANSFER INTERFACE

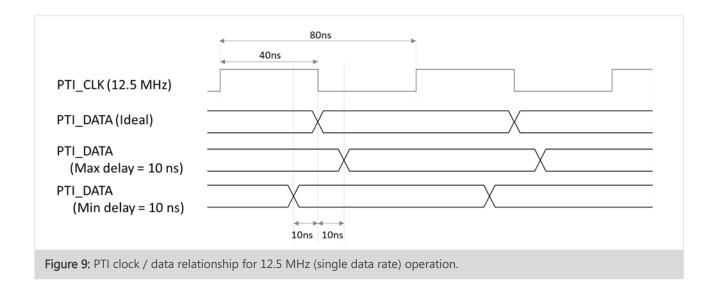

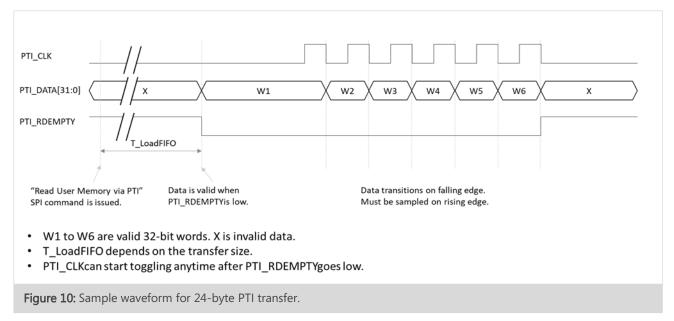

The SV3D includes a low-speed, 32 bit wide output parallel interface, for transferring data from the SV3D to a DUT or external device. Data on the 32 bit interface is valid when the PTI\_RDEMPTY output pin is low and valid on the rising edge of PTI\_CLK input (clock signal provided by the external device). The intended rate of data transfers is 12.5 MHz. Typical transfer waveforms are given in Figure 9 and Figure 10. The pin locations for the Parallel Transfer Interface are as given in Table 6.

#### STANDARD ERROR DETECTOR ANALYSIS

The SV3D09 instrument has an independent Bit Error Rate Tester (BERT) for each of its input channels. Each BERT compares recovered (retimed) data from a single input channel against a specified data pattern and reports the bit error count.

Apart from error counting, the instrument offers a wide range of measurement and analysis features including:

- Jitter separation

- Eye mask testing

- Voltage level, pre-emphasis level, and signal parameter measurement

- Frequency measurement and SSC profile extraction

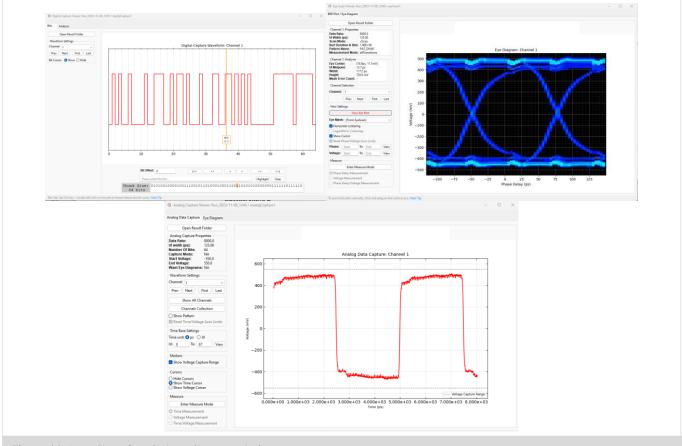

Figure 11 illustrates a few of the analysis and reporting features of the SV3D. Starting from the top left and moving in a clockwise manner, the figure illustrates bathtub acquisition and analysis, waveform capture, raw data viewing, and eye diagram plotting. As always, these analysis options are executed in parallel on all activated lanes.

Figure 11: Sampling of analysis and report windows.

#### **AUTOMATION**

The SV3D is operated using the award winning Pinetree Software. It features a comprehensive scripting language with an intuitive component-based design as shown in the screen shot in Figure 12(a). Component-based design is Pinetree's way of organizing the flexibility of the instrument in a manner that allows for easy program development. It highlights to the user only the parameters that are needed for any given task, thus allowing program execution in a matter of minutes. For further help, the SV3D features automatic code generation for common tasks such as Eye Diagram or Bathtub Curve generation as shown in Figure 12(b).

# **Physical Description**

Figure 13 and 14 depict the top and bottom views of the SV3D module.

Figure 13: Top view of SV3D module.

Figure 14: Bottom view of SV3D module.

#### LOAD BOARD CONNECTORS FOOTPRINT AND DIMENSIONS

Figure 15 depicts the connectors footprint required to mate with the SV3D module. The rectangle area is occupied by the SV3D module, to be mounted on the load board by 2 diagonal mounting holes and 5 connectors J1, J2, J3, J4 and J5.

Figure 16: SV3D side profile on load board. Measurements are in mil.

The connector part number information is shown in Table 1.

#### TABLE 1 LOADBOARD CONNECTORS DESCRIPTIONS

| CONNECTOR      | MANUFACTURER | PART<br>NUMBER           | DESCRIPTIONS                     | PIN COUNT |

|----------------|--------------|--------------------------|----------------------------------|-----------|

| J1, J2, J3, J4 | Molex        | 171446-0115              | SPEEDSTACK<br>PLUG               | 60        |

| J5             | Samtec       | SEAM8-30-02.0-<br>S-06-3 | CONN SEARAY<br>30x6, 0.8mm pitch | 180       |

# **Electrical Description**

The following tables describe the pin out information of the 5 connectors on the SV3D depicted in Figure 15. When designing the interface logic, please ensure not to drive any I/O pins on the SV3D until the power rails have been completely powered on.

TABLE 2 LOAD BOARD J1 CONNECTOR PIN-OUT

| PIN                                                           | NET      | DESCRIPTION                                      | VOLTAGE<br>LEVEL |

|---------------------------------------------------------------|----------|--------------------------------------------------|------------------|

| 1,4,7,10,13,17,20,23,26,29,32,<br>35,38,41,44,48, 51,54,57,60 | GND      |                                                  |                  |

| 2                                                             | RX17_P   | GXB Receive Link                                 | 1.5V PCML        |

| 3                                                             | RX17_N   | GXB Receive Link                                 | 1.5V PCML        |

| 5                                                             | RX21_P   | GXB Receive Link                                 | 1.5V PCML        |

| 6                                                             | RX21_N   | GXB Receive Link                                 | 1.5V PCML        |

| 8                                                             | RX18_P   | GXB Receive Link                                 | 1.5V PCML        |

| 9                                                             | RX18_N   | GXB Receive Link                                 | 1.5V PCML        |

| 11                                                            | (RX19_P) | GXB Receive Link, not present in SV3D09 firmware | 1.5V PCML        |

|                                                               |          | GXB Receive Link, not present in SV3D09          | 1.5V PCML        |

| 12                                                            | (RX19_N) | firmware                                         |                  |

| 14                                                            | RESERVED | (Not used, install R=0□ to gnd)                  | 1.5V PCML        |

| 15                                                            | RESERVED | (Not used, install R=0□ to gnd)                  | 1.5V PCML        |

| 16 | JTAG-TMS | Built-in Pull-up Resistor10kOhm         | 2.5V      |

|----|----------|-----------------------------------------|-----------|

| 18 | RX20_P   | GXB Receive Link                        | 1.5V PCML |

| 19 | RX20_N   | GXB Receive Link                        | 1.5V PCML |

| 21 | RX24_N   | GXB Receive Link                        | 1.5V PCML |

| 22 | RX24_P   | GXB Receive Link                        | 1.5V PCML |

| 24 | RX23_N   | GXB Receive Link                        | 1.5V PCML |

| 25 | RX23_P   | GXB Receive Link                        | 1.5V PCML |

|    |          | GXB Receive Link, not present in SV3D09 | 1.5V PCML |

| 27 | (RX22_N) | firmware                                |           |

|    |          | GXB Receive Link, not present in SV3D09 | 1.5V PCML |

| 28 | (RX22_P) | firmware                                |           |

| 30 | JTAG-TCK | Built-in Pull-up Resistor 1kOhm         | 2.5V      |

| 31 | JTAG-TDI | Built-in Pull-up Resistor 10kOhm        | 2.5V      |

| 33 | TX17_P   | GXB Transmit Link                       | 1.5V PCML |

| 34 | TX17_N   | GXB Transmit Link                       | 1.5V PCML |

| 36 | TX21_P   | GXB Transmit Link                       | 1.5V PCML |

| 37 | TX21_N   | GXB Transmit Link                       | 1.5V PCML |

| 39 | TX18_N   | GXB Transmit Link                       | 1.5V PCML |

| 40 | TX18_P   | GXB Transmit Link                       | 1.5V PCML |

| 42 | TX19_P   | GXB Transmit Link                       | 1.5V PCML |

| 43 | TX19_N   | GXB Transmit Link                       | 1.5V PCML |

| 45 | JTAG-TDO | Built-in Pull-up Resistor 21.5kOhm      | 2.5V      |

| 46 | RESERVED | (Not used, install R=0□ to gnd)         | 1.5V PCML |

| 47 | RESERVED | (Not used, install R=0□ to gnd)         | 1.5V PCML |

| 49 | TX20_N   | GXB Transmit Link                       | 1.5V PCML |

| 50 | TX20_P   | GXB Transmit Link                       | 1.5V PCML |

| 52 | TX24_P   | GXB Transmit Link                       | 1.5V PCML |

| 53 | TX24_N   | GXB Transmit Link                       | 1.5V PCML |

| 55 | TX23_N   | GXB Transmit Link                       | 1.5V PCML |

| 56 | TX23_P   | GXB Transmit Link                       | 1.5V PCML |

| 58 | TX22_P   | GXB Transmit Link                       | 1.5V PCML |

| 59 | TX22_N   | GXB Transmit Link                       | 1.5V PCML |

TABLE 3 LOAD BOARD J2 CONNECTOR PIN-OUT

| PIN                            | NET        | DESCRIPTION                                      | VOLTAGE<br>LEVEL |

|--------------------------------|------------|--------------------------------------------------|------------------|

| 1,4,7,10,13,17,20,23,26,29,32, |            |                                                  |                  |

| 35,38,41,44,48, 51,54,57,60    | GND        |                                                  |                  |

| 2                              | RX25_P     | GXB Receive Link                                 | 1.5V PCML        |

| 3                              | RX25_N     | GXB Receive Link                                 | 1.5V PCML        |

| 5                              | RX29_P     | GXB Receive Link                                 | 1.5V PCML        |

| 6                              | RX29_N     | GXB Receive Link                                 | 1.5V PCML        |

| 8                              | RX26_P     | GXB Receive Link                                 | 1.5V PCML        |

| 9                              | RX26_N     | GXB Receive Link                                 | 1.5V PCML        |

|                                | (RX30_N)   | GXB Receive Link, not present in SV3D09          | 1.5V PCML        |

| 11                             |            | firmware                                         |                  |

|                                | (RX30_P)   | GXB Receive Link, not present in SV3D09          | 1.5V PCML        |

| 12                             |            | firmware                                         |                  |

| 14                             | RESERVED   | (Not used, install R=0□ to gnd)                  | 1.5V PCML        |

| 15                             | RESERVED   | (Not used, install R=0 <sub>0</sub> to gnd)      | 1.5V PCML        |

| 16                             | EXTRA_IO_1 | GPIO pin                                         | 2.5V LVCMOS      |

| 18                             | RX27_P     | GXB Receive Link                                 | 1.5V PCML        |

| 19                             | RX27_N     | GXB Receive Link                                 | 1.5V PCML        |

| 21                             | RX31_P     | GXB Receive Link                                 | 1.5V PCML        |

| 22                             | RX31_N     | GXB Receive Link                                 | 1.5V PCML        |

| 24                             | RX28_P     | GXB Receive Link                                 | 1.5V PCML        |

| 25                             | RX28_N     | GXB Receive Link                                 | 1.5V PCML        |

| 27                             | (RX32_N)   | GXB Receive Link, not present in SV3D09 firmware | 1.5V PCML        |

|                                | (RX32_P)   | GXB Receive Link, not present in SV3D09          | 1.5V PCML        |

| 28                             |            | firmware                                         |                  |

| 30                             | EXTRA_IO_3 | GPIO pin                                         | 2.5V LVCMOS      |

| 31                             | EXTRA_IO_0 | GPIO pin                                         | 2.5V LVCMOS      |

| 33                             | TX25_N     | GXB Transmit Link                                | 1.5V PCML        |

| 34                             | TX25_P     | GXB Transmit Link                                | 1.5V PCML        |

| 36                             | TX29_P     | GXB Transmit Link                                | 1.5V PCML        |

| 37                             | TX29_N     | GXB Transmit Link                                | 1.5V PCML        |

| 39                             | TX26_N     | GXB Transmit Link                                | 1.5V PCML        |

| 40                             | TX26_P     | GXB Transmit Link                                | 1.5V PCML        |

| 42                             | TX30_P     | GXB Transmit Link                                | 1.5V PCML        |

| 43                             | TX30_N     | GXB Transmit Link                                | 1.5V PCML        |

| 45                             | RESERVED   | (Not used, install R=0 <sub>n</sub> to gnd)      | 1.5V PCML        |

| 46                             | RESERVED   | (Not used, install R=0 <sub>0</sub> to gnd)      | 1.5V PCML        |

| 47                             | EXTRA_IO_2 | GPIO pin                                         | 2.5V LVCMOS      |

| 49 | TX27_N | GXB Transmit Link | 1.5V PCML |

|----|--------|-------------------|-----------|

| 50 | TX27_P | GXB Transmit Link | 1.5V PCML |

| 52 | TX31_P | GXB Transmit Link | 1.5V PCML |

| 53 | TX31_N | GXB Transmit Link | 1.5V PCML |

| 55 | TX28_N | GXB Transmit Link | 1.5V PCML |

| 56 | TX28_P | GXB Transmit Link | 1.5V PCML |

| 58 | TX32_P | GXB Transmit Link | 1.5V PCML |

| 59 | TX32_N | GXB Transmit Link | 1.5V PCML |

TABLE 4 LOAD BOARD J3 CONNECTOR PIN-OUT

| PIN                            | NET        | DESCRIPTION                                  | VOLTAGE<br>LEVEL |

|--------------------------------|------------|----------------------------------------------|------------------|

| 1,4,7,10,13,17,20,23,26,29,32, |            |                                              |                  |

| 35,38,41,44,48, 51,54,57,60    | GND        |                                              |                  |

| 2                              | TX1_P      | GXB Transmit Link                            | 1.5V PCML        |

| 3                              | TX1_N      | GXB Transmit Link                            | 1.5V PCML        |

| 5                              | TX2_P      | GXB Transmit Link                            | 1.5V PCML        |

| 6                              | TX2_N      | GXB Transmit Link                            | 1.5V PCML        |

| 8                              | TX3_N      | GXB Transmit Link                            | 1.5V PCML        |

| 9                              | TX3_P      | GXB Transmit Link                            | 1.5V PCML        |

| 11                             | TX4_P      | GXB Transmit Link                            | 1.5V PCML        |

| 12                             | TX4_N      | GXB Transmit Link                            | 1.5V PCML        |

| 14                             | EXTRA_IO_5 | Master and Slave Cores Locked. Active Low    | 2.5V LVCMOS      |

| 15                             | RESERVED   | (Not used, install R=0□ to gnd)              | 1.5V PCML        |

| 16                             | RESERVED   | (Not used, install R=0□ to gnd)              | 1.5V PCML        |

| 18                             | TX8_N      | GXB Transmit Link                            | 1.5V PCML        |

| 19                             | TX8_P      | GXB Transmit Link                            | 1.5V PCML        |

| 21                             | TX7_N      | GXB Transmit Link                            | 1.5V PCML        |

| 22                             | TX7_P      | GXB Transmit Link                            | 1.5V PCML        |

| 24                             | TX6_N      | GXB Transmit Link                            | 1.5V PCML        |

| 25                             | TX6_P      | GXB Transmit Link                            | 1.5V PCML        |

| 27                             | TX5_N      | GXB Transmit Link                            | 1.5V PCML        |

| 28                             | TX5_P      | GXB Transmit Link                            | 1.5V PCML        |

| 30                             | EXTRA_IO_7 | GPIO pin                                     | 2.5V LVCMOS      |

| 31                             | EXTRA_IO_4 | User LED and Tx Buffer Underflow. Active Low | 2.5V LVCMOS      |

| 33                             | RX1_P      | GXB Receive Link                             | 1.5V PCML        |

| 34                             | RX1_N      | GXB Receive Link                             | 1.5V PCML        |

| 36                             | RX2_N      | GXB Receive Link                             | 1.5V PCML        |

| 37 | RX2_P      | GXB Receive Link                                 | 1.5V PCML   |

|----|------------|--------------------------------------------------|-------------|

| 39 | RX3_P      | GXB Receive Link                                 | 1.5V PCML   |

| 40 | RX3_N      | GXB Receive Link                                 | 1.5V PCML   |

| 42 | (RX4_N)    | GXB Receive Link, not present in SV3D09 firmware | 1.5V PCML   |

| 43 | (RX4_P)    | GXB Receive Link, not present in SV3D09 firmware | 1.5V PCML   |

| 45 | EXTRA_IO_6 | Master and Slave Cores Ready. Active Low         | 2.5V LVCMOS |

| 46 | RESERVED   | (Not used, install R=0□ to gnd)                  | 1.5V PCML   |

| 47 | RESERVED   | (Not used, install R=0□ to gnd)                  | 1.5V PCML   |

| 49 | RX8_P      | GXB Receive Link                                 | 1.5V PCML   |

| 50 | RX8_N      | GXB Receive Link                                 | 1.5V PCML   |

| 52 | RX7_N      | GXB Receive Link                                 | 1.5V PCML   |

| 53 | RX7_P      | GXB Receive Link                                 | 1.5V PCML   |

| 55 | RX6_P      | GXB Receive Link                                 | 1.5V PCML   |

| 56 | RX6_N      | GXB Receive Link                                 | 1.5V PCML   |

| 58 | (RX5_N)    | GXB Receive Link, not present in SV3D09 firmware | 1.5V PCML   |

| 59 | (RX5_P)    | GXB Receive Link, not present in SV3D09 firmware | 1.5V PCML   |

### TABLE 5 LOAD BOARD J4 CONNECTOR PIN-OUT

| PIN                            | NET         | DESCRIPTION       | VOLTAGE<br>LEVEL |

|--------------------------------|-------------|-------------------|------------------|

| 1,4,7,10,13,17,20,23,26,29,32, |             |                   |                  |

| 35,38,41,44,48, 51,54,57,60    | GND         |                   |                  |

| 2                              | TX9_P       | GXB Transmit Link | 1.5V PCML        |

| 3                              | TX9_N       | GXB Transmit Link | 1.5V PCML        |

| 5                              | TX10_P      | GXB Transmit Link | 1.5V PCML        |

| 6                              | TX10_N      | GXB Transmit Link | 1.5V PCML        |

| 8                              | TX14_N      | GXB Transmit Link | 1.5V PCML        |

| 9                              | TX14_P      | GXB Transmit Link | 1.5V PCML        |

| 11                             | TX13_N      | GXB Transmit Link | 1.5V PCML        |

| 12                             | TX13_P      | GXB Transmit Link | 1.5V PCML        |

| 14                             | REFIN_CLK_P | Ref Clock Input   | 3.3V LVDS*       |

| 15                             | REFIN_CLK_N | Ref Clock Input   | 3.3V LVDS*       |

| 16                             | EXTRA_IO_9  | GPIO pin          | 2.5V LVCMOS      |

| 18                             | TX11_P      | GXB Transmit Link | 1.5V PCML        |

| 19                             | TX11_N      | GXB Transmit Link | 1.5V PCML        |

| 21                             | TX15_P      | GXB Transmit Link | 1.5V PCML        |

| 22                             | TX15_N      | GXB Transmit Link | 1.5V PCML        |

| 24 | TX12 P      | GXB Transmit Link                           | 1.5V PCML   |

|----|-------------|---------------------------------------------|-------------|

| 25 | TX12_N      | GXB Transmit Link                           | 1.5V PCML   |

| 27 | TX16_N      | GXB Transmit Link                           | 1.5V PCML   |

| 28 | TX16 P      | GXB Transmit Link                           | 1.5V PCML   |

| 30 | EXTRA_IO_11 | GPIO pin                                    | 2.5V LVCMOS |

| 31 | EXTRA_IO_8  | GPIO pin                                    | 2.5V LVCMOS |

| 33 | RX9 P       | GXB Receive Link                            | 1.5V PCML   |

| 34 | RX9 N       | GXB Receive Link                            | 1.5V PCML   |

| 36 | RX10 N      | GXB Receive Link                            | 1.5V PCML   |

| 37 | RX10 P      | GXB Receive Link                            | 1.5V PCML   |

| 39 | RX14 P      | GXB Receive Link                            | 1.5V PCML   |

| 40 | RX14_N      | GXB Receive Link                            | 1.5V PCML   |

| -  | (RX13_N)    | GXB Receive Link, not present in SV3D09     | 1.5V PCML   |

| 42 |             | firmware                                    |             |

|    | (RX13_P)    | GXB Receive Link, not present in SV3D09     | 1.5V PCML   |

| 43 |             | firmware                                    |             |

| 45 | EXTRA_IO_10 | GPIO pin                                    | 2.5V LVCMOS |

| 46 | RESERVED    | (Not used, install R=0 <sub>□</sub> to gnd) | 1.5V PCML   |

| 47 | RESERVED    | (Not used, install R=0 <sub>□</sub> to gnd) | 1.5V PCML   |

| 49 | RX11_N      | GXB Receive Link                            | 1.5V PCML   |

| 50 | RX11_P      | GXB Receive Link                            | 1.5V PCML   |

| 52 | RX15_P      | GXB Receive Link                            | 1.5V PCML   |

| 53 | RX15_N      | GXB Receive Link                            | 1.5V PCML   |

| 55 | RX12_N      | GXB Receive Link                            | 1.5V PCML   |

| 56 | RX12_P      | GXB Receive Link                            | 1.5V PCML   |

|    | (RX16_P)    | GXB Receive Link, not present in SV3D09     | 1.5V PCML   |

| 58 |             | firmware                                    |             |

|    | (RX16_N)    | GXB Receive Link, not present in SV3D09     | 1.5V PCML   |

| 59 |             | firmware                                    |             |

TABLE 6 LOAD BOARD J5 CONNECTOR PIN-OUT\*

| Z  | Z E T          | 0/1 | Z  | N E T                   | 0/1 | NIG | <b>Н</b><br>Ш<br>Z    | 1/0 |

|----|----------------|-----|----|-------------------------|-----|-----|-----------------------|-----|

| 1  | 12V0           |     | 61 | PTI_RESET_N             | I   | 121 | GPIO_1_0 /<br>FLAG[3] | I/O |

| 2  | 12V0           |     | 62 | GPIO_4_4 /<br>Reserved  | I   | 122 | GPIO_1_7              |     |

| 3  | 12V0           |     | 63 | GPIO_4_11<br>/ Reserved | I   | 123 | GND                   |     |

| 4  | 12V0           |     | 64 | GPIO_4_12<br>/ Reserved | 0   | 124 | GPIO_2_12             |     |

| 5  | 12V0           |     | 65 | GPIO_4_19<br>/ Reserved | I   | 125 | GPIO_2_19             |     |

| 6  | 12V0           |     | 66 | GND                     |     | 126 | GPIO_2_20             |     |

| 7  | GND            |     | 67 | GPIO_3_0 /<br>Reserved  | I   | 127 | GPIO_1_1              |     |

| 8  | GND            |     | 68 | GPIO_3_7 /<br>Reserved  | I   | 128 | GND                   |     |

| 9  | GND            |     | 69 | GPIO_3_8 /<br>Reserved  | 0   | 129 | GPIO_DQS_1<br>8       |     |

| 10 | GND            |     | 70 | GPIO_3_15<br>/ Reserved | I   | 130 | GPIO_1_15             |     |

| 11 | GND            |     | 71 | GND                     |     | 131 | GPIO_1_16             |     |

| 12 | GND            |     | 72 | GPIO_4_20<br>/ Reserved | I   | 132 | GPIO_1_23             |     |

| 13 | PTI_DATA_<br>0 | I/O | 73 | GPIO_3_1                |     | 133 | GND                   |     |

| 14 | PTI_DATA_<br>1 | I/O | 74 | GPIO_3_6                |     | 134 | GPIO_1_6              |     |

| 15 | PTI_DATA_<br>2 | I/O | 75 | GPIO_3_9                |     | 135 | GPIO_1_9              |     |

| 16 | PTI_DATA_<br>3 | I/O | 76 | GND                     |     | 136 | GPIO_1_14             |     |

| 17 | PTI_DATA_<br>4 | I/O | 77 | GPIO_3_16               |     | 137 | GPIO_1_17             |     |

| 18 | PTI_DATA_         | I/O | 78 | GPIO_3_23         | 138 | GPIO_1_22                 |     |

|----|-------------------|-----|----|-------------------|-----|---------------------------|-----|

| 19 | PTI_DATA_         | I/O | 79 | GPIO_3_2          | 139 | GPIO_1_2 /<br>EXT_TRIG[1] | I   |

| 20 | PTI_DATA_<br>7    | I/O | 80 | GPIO_DQS_<br>3_5  | 140 | GPIO_1_5 /<br>FLAG[2]     | I/O |

| 21 | PTI_DATA_<br>8    | I/O | 81 | GND               | 141 | GPIO_1_10                 |     |

| 22 | GPIO_DQS_<br>5_13 |     | 82 | GPIO_3_14         | 142 | GPIO_DQS_1<br>_13         |     |

| 23 | GPIO_5_17         |     | 83 | GPIO_DQS_<br>3_17 | 143 | GPIO_1_18                 |     |

| 24 | GND               |     | 84 | GPIO_3_22         | 144 | GPIO_1_21                 |     |

| 25 | PTI_DATA_<br>9    | I/O | 85 | GPIO_3_3          | 145 | GPIO_1_3 /<br>FLAG[1]     | I/O |

| 26 | PTI_DATA_<br>10   | I/O | 86 | GND               | 146 | GPIO_1_4 /<br>FLAG[0]     | I/O |

| 27 | PTI_DATA_<br>11   | I/O | 87 | GPIO_3_10         | 147 | GPIO_1_11                 |     |

| 28 | PTI_DATA_<br>12   | I/O | 88 | GPIO_3_13         | 148 | GPIO_1_12                 |     |

| 29 | GND               |     | 89 | GPIO_3_18         | 149 | GPIO_1_19                 |     |

| 30 | PTI_DATA_<br>13   | I/O | 90 | GPIO_3_21         | 150 | GND                       |     |

| 31 | PTI_DATA_<br>14   | I/O | 91 | GND               | 151 | SCLK_R                    | I   |

| 32 | PTI_DATA_<br>15   | I/O | 92 | GPIO_3_4          | 152 | MOSI_R                    | I   |

| 33 | PTI_DATA_<br>16   | I/O | 93 | GPIO_3_11         | 153 | GPIO_0_8                  |     |

| 34 | GND               |     | 94 | GPIO_3_12         | 154 | SS_n_L                    | I   |

| 35 | PTI_DATA_<br>17   | I/O | 95 | GPIO_3_19         | 155 | GND                       |     |

| 36 | PTI_DATA_<br>18   | I/O | 96 | GPIO_3_20         | 156 | GPIO_1_20                 |     |

| 37 | PTI_DATA_<br>19   | I/O | 97 | GPIO_2_0          | 157 | MISO_R                    | 0   |

| 38 | PTI_DATA_<br>20   | I/O | 98 | GPIO_DQS_<br>2_7  | 158 | SS_n_R                    | I   |

| 39 | GND               |     | 99 | GPIO_2_8          | 159 | GPIO_DQS_0<br>_9          |     |

| 40 | PTI_DATA_            | I/O | 100 | GPIO_2_15                |           | 160 | GND               |   |

|----|----------------------|-----|-----|--------------------------|-----------|-----|-------------------|---|

| 41 | PTI_DATA_            | I/O | 101 | GPIO_2_16                |           | 161 | MOSI_L            | 1 |

| 42 | PTI_DATA_            | I/O | 102 | CDIO 2 22                | GPIO_2_23 |     | CDIO 0 22         |   |

| 42 | 23                   | 1/0 | 102 | GPIO_2_23                |           | 162 | GPIO_0_23         |   |

| 43 | PTI_DATA_<br>24      | I/O | 103 | GPIO_2_1                 |           | 163 | GPIO_0_2          |   |

| 44 | GND                  |     | 104 | GPIO_2_6                 |           | 164 | GPIO_0_5          |   |

| 45 | PTI_DATA_<br>25      | I/O | 105 | GPIO_2_9                 |           | 165 | GND               |   |

| 46 | PTI_DATA_<br>26      | I/O | 106 | GPIO_DQS_<br>2 14        |           | 166 | SCLK_L            | I |

| 47 | PTI_DATA_<br>27      | I/O | 107 | GPIO_2_17                |           | 167 | MISO_L            | 0 |

| 48 | PTI_DATA_<br>28      | I/O | 108 | GND                      |           | 168 | GPIO_0_22         |   |

| 49 | GND                  |     | 109 | GPIO_2_2                 |           | 169 | GPIO_0_3          |   |

| 50 | PTI_DATA_<br>29      | I/O | 110 | GPIO_2_5                 |           | 170 | GND               |   |

| 51 | PTI_DATA_<br>30      | I/O | 111 | GPIO_2_10                |           | 171 | GPIO_0_10         |   |

| 52 | PTI_DATA_<br>31      | I/O | 112 | GPIO_2_13                |           | 172 | GPIO_0_13         |   |

| 53 | PTI_CLK              |     | 113 | GND                      |           | 173 | GPIO_0_18         |   |

| 54 | PTI_WRRE<br>Q_N      | I   | 114 | GPIO_2_22                |           | 174 | GPIO_0_21         |   |

| 55 | PTI_RDREQ<br>_N      | I   | 115 | GPIO_2_3 /<br>EXT_TRIG[0 | I         | 175 | GND               |   |

| 56 | PTI_WR_N             | 0   | 116 | GPIO_2_4 /<br>FLAG[4]    | l/<br>O   | 176 | GPIO_0_4          |   |

| 57 | PTI_RD_N             | 0   | 117 | GPIO_2_11                |           | 177 | GPIO_0_11         |   |

| 58 | CMD_PRO<br>C_READY_A | 0   | 118 | GND                      |           | 178 | GPIO_0_12         |   |

| 59 | CMD_PRO<br>C_READY_B | 0   | 119 | GPIO_2_18                |           | 179 | SV3_RST_N         | I |

| 60 | PTI_OE_N             | 0   | 120 | GPIO_2_21                |           | 180 | GPIO_DQS_0<br>_20 |   |

# Specifications

### TABLE 7 GENERAL SPECIFICATIONS

| PARAMETER                           | VALUE | UNITS | DESCRIPTION AND CONDITIONS                                |

|-------------------------------------|-------|-------|-----------------------------------------------------------|

| Ports                               |       |       |                                                           |

| Number of Differential Transmitters | 32    |       | See Table 2 to Table 5 for Pinout.                        |

| Number of Differential Receivers    | 24    |       | See Table 2 to Table 5 for Pinout.                        |

| Number of Dedicated Clock Inputs    | 1     |       | Used as external Reference Clock input. See Table 5 for   |

|                                     |       |       | pinout.                                                   |

| Number of Trigger Input Pins        | 2     |       | Consult user manual for included capability. See Table 6  |

|                                     |       |       | for pinout.                                               |

| Number of Flag Output Pins          | 5     |       | Consult user manual for included capability. See Table 5  |

|                                     |       |       | for pinout.                                               |

| Generic I/O Pins                    | 190   |       | Consult user manual for included capability. See Table 3  |

|                                     |       |       | to Table 6 for pinout. Contact factory for customization. |

| TX Channel Groups                   |       |       |                                                           |

| Number of independent TX groups     | 8     |       | TX jitter injection and TX fine skew control are applied  |

|                                     |       |       | within each in the following independent channel          |

|                                     |       |       | groupings:                                                |

|                                     |       |       | Group 1: 1,2,3,4                                          |

|                                     |       |       | Group 2: 5, 6, 7, 8                                       |

|                                     |       |       | Group 3: 9, 10, 13, 14                                    |

|                                     |       |       | Group 4: 11, 12, 15, 16                                   |

|                                     |       |       | Group 5:17, 18, 19, 21                                    |

|                                     |       |       | Group 6: 20, 22, 23, 24                                   |

|                                     |       |       | Group 7: 25, 26, 29, 30                                   |

|                                     |       |       | Group 8: 27, 28, 31, 32                                   |

|                                     |       |       | See Table 2 to Table 5 for pinout.                        |

| Data Rates and Frequencies          |       |       |                                                           |

| Minimum Programmable Data Rate      | 400   | Mbps  | Contact factory for extension to lower data rates.        |

| Maximum Programmable Data Rate      | 12.8  | Gbps  |                                                           |

| Frequency Resolution of Programmed  | 1     | kHz   | Finer resolution is possible. Contact factory for         |

| Data Rate                           |       |       | customization.                                            |

| Minimum External Input Clock        | 25    | MHz   |                                                           |

| Frequency                           |       |       |                                                           |

| Maximum External Input Clock        | 250   | MHz   |                                                           |

| frequency                           |       |       |                                                           |

| Supported External Input Clock I/O  |       |       | LVDS (typical 400 mVpp input)                             |

| Standards                           |       |       | LVPECL (typical 800 mVpp input)                           |

| Voltage and Current Ratings and Operating Conditions |     |   |                                                          |

|------------------------------------------------------|-----|---|----------------------------------------------------------|

| Voltage Supply                                       | 12  | V | See Table 6 for pinout connections.                      |

| Current on 12V DC input                              | 2.9 | Α | Typical power-up condition:                              |

|                                                      |     |   | -Tx and Rx lanes idle                                    |

|                                                      |     |   |                                                          |

|                                                      | 3.3 | Α | Typical operating condition:                             |

|                                                      |     |   | - All 32 Tx cannels running at 8 Gbps                    |

|                                                      |     |   | - All 32 Rx channels running BER checking as well as eye |

|                                                      |     |   | diagram measurement at 8 Gbps                            |

|                                                      | 5.6 | Α | Maximum operating condition:                             |

|                                                      |     |   | - All 32 Tx pairs running at maximum data rate           |

|                                                      |     |   | - All 32 Rx pairs running BER checking as well as eye    |

|                                                      |     |   | diagram measurement at maximum data rate                 |

### TABLE 8 TRANSMITTER CHARACTERISTICS

| PARAMETER                              | VALUE                                                           | UNITS        | DESCRIPTION AND CONDITIONS                                                                               |

|----------------------------------------|-----------------------------------------------------------------|--------------|----------------------------------------------------------------------------------------------------------|

| Output Standard                        |                                                                 |              | CONDITIONS                                                                                               |

| I/O Standard                           |                                                                 |              | PCML (Current Mode Logic)                                                                                |

| DC common mode voltage                 | 750                                                             | mV           | Typical (firmware programmable to VOD/2)                                                                 |

| AC Output Differential Impedance       | 100                                                             | Ohm          | Typical                                                                                                  |

| Voltage Performance                    |                                                                 |              |                                                                                                          |

| Minimum Differential Voltage Swing     | 20                                                              | mV           |                                                                                                          |

| Maximum Differential Voltage Swing     | 1000<br>800                                                     | mVpp<br>mVpp | 400 Mbps to 5 Gbps, 50 ohm, AC coupled termination. 5 Gbps to 12.8 Gbps, 50 ohm, AC coupled termination. |

| Differential Voltage Swing Resolution  | 20                                                              | mV           |                                                                                                          |

| Accuracy of Differential Voltage Swing | larger of: +/-<br>10% of<br>programmed<br>value, and<br>+/-20mV | %, mV        |                                                                                                          |

| Rise and Fall Time                     | 50                                                              | ps           | 500 mVpp signal, 20-80%, 50 ohm AC coupled termination.                                                  |

| Pre-emphasis Performance               |                                                                 |              |                                                                                                          |

| Pre-Emphasis Pre-Tap Range                            | -4 to +4   | dB  | Both high-pass and low-pass functions are available. This is the smallest achievable range based on worst-case conditions. Typical operating conditions result in wider pre-emphasis range. |

|-------------------------------------------------------|------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pre-Emphasis Pre-Tap Resolution                       | Range / 32 | dB  |                                                                                                                                                                                             |

| Pre-Emphasis Post1-Tap Range                          | 0 to 6     | dB  | Only high-pass function is available. This is the smallest achievable range based on worst-case conditions. Typical operating conditions result in wider pre-emphasis range.                |

| Pre-Emphasis Post1-Tap Resolution                     | Range / 32 | dB  |                                                                                                                                                                                             |

| Pre-Emphasis Post2-Tap Range                          | -4 to +4   | dB  | Both high-pass and low-pass functions are available. This is the smallest achievable range based on worst-case conditions. Typical operating conditions result in wider pre-emphasis range. |

| Pre-Emphasis Post2-Tap Resolution                     | Range / 32 | dB  |                                                                                                                                                                                             |

| Jitter Performance                                    |            |     |                                                                                                                                                                                             |

| Random Jitter Noise Floor                             | 1          | ps  | Based on a single-lane measurement with high-bandwidth scope and with first-order clock recovery.                                                                                           |

| Minimum Frequency of Injected Deterministic Jitter    | 0.1        | kHz | Contact factory for further customization.                                                                                                                                                  |

| Maximum Frequency of Injected Deterministic Jitter    | 20         | MHz |                                                                                                                                                                                             |

| Frequency Resolution of Injected Deterministic Jitter | 0.1        | kHz | Contact factory for further customization.                                                                                                                                                  |

| Maximum Peak-to-Peak Injected Deterministic           | 1200       | ps  | at 1 MHz                                                                                                                                                                                    |

| Jitter                                                | 500        | ps  | at 5 MHz                                                                                                                                                                                    |

|                                                       | 300        | ps  | at 10 MHz                                                                                                                                                                                   |

|                                                       | 100        | ps  | at 20 MHz (This specification is separate from low-frequency wander generator and SSC generator.)                                                                                           |

| Magnitude Resolution of Injected Deterministic Jitter | 500        | fs  | Jitter injection is based on multi-<br>resolution synthesizer, so this number is<br>an effective resolution. Internal<br>synthesizer resolution is defined in<br>equivalent number of bits. |

| Injected Deterministic Jitter Setting                 | Per-group  |     | Common across all channels within a group.                                                                                                                                                  |

| Maximum RMS Random Jitter Injection                   | 0.1        | UI  |                                                                                                                                                                                             |

| Magnitude Resolution of Injected Jitter        | 0.1                      | ps          |                                                                                                                                             |

|------------------------------------------------|--------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Accuracy of Injected Jitter Magnitude          | larger of: +/-<br>10% of | %, ps       |                                                                                                                                             |

|                                                | programmed               |             |                                                                                                                                             |

|                                                | value, and               |             |                                                                                                                                             |

|                                                | +/-10 ps                 |             |                                                                                                                                             |

| Injected Random Jitter Setting                 | Common                   |             | Common across all channels within a TX                                                                                                      |

|                                                |                          |             | group.                                                                                                                                      |

| Transmitter-to-Transmitter Skew Performance    |                          |             |                                                                                                                                             |

| Lane to Lane Integer-UI Minimum Skew Injection | -20                      | UI          |                                                                                                                                             |

| Lane to Lane Integer-UI Maximum Skew Injection | 20                       | UI          |                                                                                                                                             |

| TX group to TX group fine skew minimum setting | -500                     | ps          |                                                                                                                                             |

| TX group to TX group fine skew maximum setting | 500                      | ps          |                                                                                                                                             |

| Effect of Skew Adjustment on Jitter Injection  | None                     |             |                                                                                                                                             |

| Lane to Lane Skew                              | +/- 15<br>+/- 0.5        | ps pp<br>UI | Peak-peak spread of master channels across groups. Peak-peak spread of non-master channels with respect to master channel within the group. |

# TABLE 9 RECEIVER CHARACTERISTICS

| PARAMETER                                               | VALUE                                                            | UNITS | DESCRIPTION AND CONDITIONS                                                                     |

|---------------------------------------------------------|------------------------------------------------------------------|-------|------------------------------------------------------------------------------------------------|

| Input Coupling                                          |                                                                  |       |                                                                                                |

| AC Input Differential Impedance                         | 100                                                              | Ohm   | This is the impedance between differential wires.  Receiver inputs are DC-coupled.             |

| AC Performance                                          |                                                                  |       |                                                                                                |

| Minimum Detectable Differential Voltage                 | 25                                                               | mV    |                                                                                                |

| Maximum Allowable Differential Voltage                  | 2000                                                             | mV    |                                                                                                |

| Minimum Programmable Comparator<br>Threshold Voltage    | -500                                                             | mV    |                                                                                                |

| Maximum Programmable Comparator<br>Threshold Voltage    | +500                                                             | mV    |                                                                                                |

| Differential Comparator Threshold Voltage<br>Resolution | 10                                                               | mV    |                                                                                                |

| Differential Comparator Threshold Voltage<br>Accuracy   | larger of: +/-<br>10% of<br>programmed<br>value, and +/-<br>20mV | %, mV |                                                                                                |

| Resolution Enhancement & Equalization                   |                                                                  |       |                                                                                                |

| DC Gain                                                 | 0, 2, 4, 6, 8                                                    | dB    |                                                                                                |

| CTLE Maximum Gain                                       | 16                                                               | dB    |                                                                                                |

| CTLE Resolution                                         | 1                                                                | dB    |                                                                                                |

| DC Gain Control                                         | Per-receiver                                                     |       |                                                                                                |

| Equalization Control                                    | Per-receiver                                                     |       |                                                                                                |

| Jitter Performance                                      |                                                                  |       |                                                                                                |

| Input Jitter Noise Floor in System Reference Mode       | 25                                                               | ps    | Based on a single-lane measurement.                                                            |

| Input Jitter Noise Floor in Extracted Clock<br>Mode     | 10                                                               | ps    | Based on a single-lane measurement.                                                            |

| Timing Generator Performance                            |                                                                  |       |                                                                                                |

| Resolution at Maximum Data Rate                         | 31.25                                                            | mUI   | Resolution (as a percentage of UI) improves for lower data rates. Contact factory for details. |

| Differential Non-Linearity Error                        | +/- 0.5                                                          | LSB   |                                                                                                |

| Integral Non-Linearity Error                            | +/- 5                                                            | ps    |                                                                                                |

| Range                                                   | Unlimited                                                        |       |                                                                                                |

| +/- 10 | ps     | Measured t 6.401 Gbps, system clock. |

|--------|--------|--------------------------------------|

|        | +/- 10 | +/- 10 ps                            |

# TABLE 10 CLOCKING CHARACTERISTICS

| PARAMETER                               | VALUE               | UNITS             | DESCRIPTION AND CONDITIONS                                                                                                                                      |

|-----------------------------------------|---------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Internal Time Base                      |                     |                   |                                                                                                                                                                 |

| Number of Internal Frequency References | 5                   |                   | Standard configuration creates one measurement path frequency reference, two output clock frequency references. Contact factory for clock domain customization. |

| Embedded Clock Applications             |                     | •                 |                                                                                                                                                                 |

| Transmit Timing Modes                   | System<br>Extracted |                   | Clock can be extracted from one of the data receiver channels in order to drive all transmitter channels.                                                       |

| Receive Timing Modes                    | System<br>Extracted |                   | All channels have clock recovery for extracted mode operation.                                                                                                  |

| Single-Lane CDR Tracking Bandwidth      | 18<br>24<br>35      | MHz<br>MHz<br>MHz | Low BW setting Medium BW setting High BW setting                                                                                                                |

| Forwarded Clock Applications            |                     | <u>'</u>          | , 5                                                                                                                                                             |

| Transmit Timing Modes                   | System<br>Forwarded |                   | Contact factory for forwarded clock routing recommendations.                                                                                                    |

| Receive Timing Modes                    | System<br>Forwarded |                   | Contact factory for forwarded clock routing recommendations.                                                                                                    |

| Clock Tracking Bandwidth                | 4                   | MHz               | Second order critically damped response.                                                                                                                        |

| Spread Spectrum Support                 |                     |                   |                                                                                                                                                                 |

| Receive Lanes Track SSC Data            | Yes                 |                   | Requires operation in extracted clock mode.                                                                                                                     |

| Transmit Lanes Generate SSC Data        | Yes                 |                   |                                                                                                                                                                 |

| Minimum Spread                          | 0.1                 | %                 |                                                                                                                                                                 |

| Maximum Spread                          | 2                   | %                 |                                                                                                                                                                 |

| Spread Programming Resolution           | 0.01                | %                 |                                                                                                                                                                 |

| Minimum Spreading Frequency             | 31.5                | kHz               |                                                                                                                                                                 |

| Maximum Spreading Frequency             | 63                  | kHz               |                                                                                                                                                                 |

# TABLE 11 PATTERN HANDLING CHARACTERISTICS

| PARAMETER                             | VALUE               | UNITS         | DESCRIPTION AND CONDITIONS             |

|---------------------------------------|---------------------|---------------|----------------------------------------|

| Loopback                              |                     |               |                                        |

| Rx to Tx Loopback Capability          | Per channel         |               | 24 RX channels available for loopback. |

|                                       | 0                   | UI            |                                        |

| Lane to Lane Latency Mismatch         |                     |               |                                        |

| Preset Patterns                       |                     |               |                                        |

| Standard Built-In Patterns            | All Zeros           |               |                                        |

|                                       | D21.5               |               |                                        |

|                                       | K28.5, K28.7        |               |                                        |

|                                       | DIV 16, 20          |               |                                        |

|                                       | DIV 40, 50          |               |                                        |

|                                       | PRBS 5, 7, 9, 11    |               |                                        |

|                                       | PRBS13, 15, 21      |               |                                        |

|                                       | PRBS 23, 31         |               |                                        |

| Pattern Choice per Transmit Channel   | Per-transmitter     |               |                                        |

| Pattern Choice per Receive Channel    | Per-receiver        |               |                                        |

| BERT Comparison Mode                  | Automatic seed      |               | Automatically aligns to PRBS data      |

| User-programmable Pattern Memory      | generation for PRBS |               | patterns.                              |

|                                       | 1                   | CD 1          | TVAA                                   |

| Total Available Memory                | 1                   | GByte<br>Mbit | TX Memory                              |

| Individual Force Pattern              | Per-transmitter     | IVIDIL        | RX Memory                              |

|                                       |                     |               |                                        |

| Individual Expected Pattern           | Per-receiver        | 1.5           |                                        |

| Minimum Pattern Segment Size          | 512                 | bits          |                                        |

| Maximum Pattern Segment Size          | 65536               | bits          |                                        |

| Pattern Sequencing                    |                     |               |                                        |

| Sequence Control                      | Loop infinite       |               |                                        |

|                                       | Loop on count       |               |                                        |

|                                       | Play to end         |               |                                        |

| Number of Sequencer Slots per Pattern | 12                  |               |                                        |

| Generator                             |                     |               |                                        |

| Maximum Loop Count per Sequencer Slot | 216 - 1             |               |                                        |

| Additional Pattern Characteristics    |                     |               |                                        |

| Pattern Switching       | Wait to end of |      | When sourcing PRBS patterns, this  |

|-------------------------|----------------|------|------------------------------------|

|                         | segment        |      | option does not exist.             |

|                         | Immediate      |      |                                    |

| Raw Data Capture Length | 8192           | bits | Memory allocation is customizable. |

|                         |                |      | Contact factory.                   |

# TABLE 12 INSTRUCTION SEQUENCE CACHE

| PARAMETER                          | VALUE        | UNITS | DESCRIPTION AND CONDITIONS |  |  |  |

|------------------------------------|--------------|-------|----------------------------|--|--|--|

| Simple Instruction Cache           |              |       |                            |  |  |  |

| Instruction Learn mode Instruction | Start        |       |                            |  |  |  |

|                                    | Stop         |       |                            |  |  |  |

|                                    | Replay       |       |                            |  |  |  |

| Advanced Instruction Cache         |              |       |                            |  |  |  |

| Local Instruction Storage          | 1M           |       |                            |  |  |  |

|                                    | Instructions |       |                            |  |  |  |

| Instruction Sequence Segments      | 1000         |       |                            |  |  |  |

### TABLE 13 DUT CONTROL CAPABILITIES

| PARAMETER                                | VALUE    | UNITS | DESCRIPTION AND CONDITIONS |  |  |  |

|------------------------------------------|----------|-------|----------------------------|--|--|--|

| DUT IEEE-1149-1 (JTAG) Port (Option)     |          |       |                            |  |  |  |

| JTAG-Port Transmit Signals               | TCK      |       |                            |  |  |  |