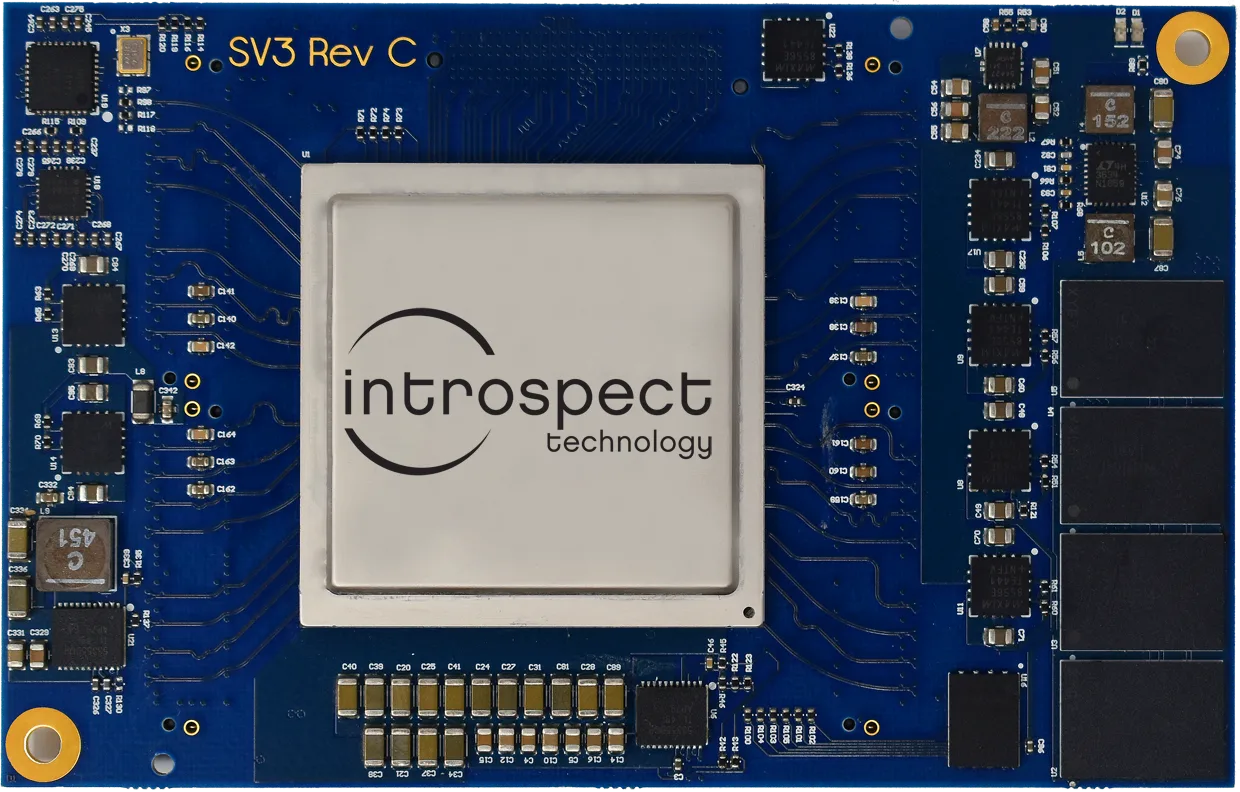

SV3D-12 Direct Attach SerDes Test Module

The SV3D-12 Direct Attach SerDes Test Module is a compact, high-performance solution designed for high-speed digital product engineering and production test environments. It enables multi-site, fully parallel testing with individual pattern generation and BER measurement per lane—ideal for system-level validation of SerDes interfaces. This self-contained module features on-board power sequencing, integrated clock synthesizers, and built-in scripting capabilities for automation and minimized test time.

Operating at data rates up to 12.5 Gbps, the SV3D-12 offers 32 independent transmitters capable of injecting sinusoidal and random jitter, applying TX de-emphasis, and introducing lane-to-lane skew. Complementing the transmitters are 32 independent receivers equipped with per-lane equalization and true parallel bit-error-rate analysis for rapid eye margin testing. With its tiny footprint and minimal I/O requirements, the SV3D-12 mounts directly on test or application boards without requiring external cabling. Communication with ATE systems is achieved via an SPI interface, with an optional parallel bus for high-volume data transfer, making it a versatile and cost-effective solution for high-throughput SerDes testing.

- Multi-site, fully parallel test capability with individual pattern and BER control per lane

- Self-contained solution with on-board power sequencers and clock synthesizers

- Automated with built-in scripting capability for test time minimization

- Tiny footprint and minimal I/O requirements

The SV3D-12 Direct Attach SerDes Test Module is highly-integrated tester that mounts directly on an application or test board without requiring cables. It satisfies the growing need for parallel, multi-site Gbps testing methodologies at the lowest possible total cost.

The SV3D-12 provides continuous data rate selection up to 12.5 Gbps. It features 32 independent transmitters with signal impairments including sinusoidal and random jitter injection, TX de-emphasis and lane-to-lane skew injection, and 32 independent receivers with per-channel equalization, true parallel bit-error-rate measurement and controls for rapid eye-margining measurement. Communication with ATE is handled seamlessly via an SPI bus and via an optional parallel interface for extended data transfers.